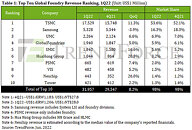

AMD Announces New Model Numbers for Future Mobile Processors

Starting next year, AMD will move to a new model number scheme for its mobile processors and it appears that the company has decided to use the first digit to represent the model year, which should alleviate some past confusion. The second digit in the model name will represent where in the product stack the specific chip will sit and here we're potentially getting some new 6 and 8 models, although nothing guarantees that AMD will actually implement these segments into real products. The third digit represents the architecture, so a four equals Zen 4 for example.

The last digit in the model names is a new addition where AMD has sub SKUs that offer some performance advantage of the base SKU of a specific model and this digit will apparently only be represented by a 0 or a 5. Finally AMD has added a new suffix too, where C stands for Chromebook. This translates to 15-28 Watt chips that have been designed specifically for Chromebook usage. The current HX, HS and U suffix lettering will carry over, alongside the lower-case e for 9 W versions the U SKUs. AMD has also segmented it's mobile CPUs according to the chart below, to try and deliver a clearer use case for its various CPU models. The chart is pretty self explanatory, although some of the segmentation will apply to updated models of current designs, whereas others will only apply to new laptop designs. The new model numbering scheme will apply to at least 2025.

The last digit in the model names is a new addition where AMD has sub SKUs that offer some performance advantage of the base SKU of a specific model and this digit will apparently only be represented by a 0 or a 5. Finally AMD has added a new suffix too, where C stands for Chromebook. This translates to 15-28 Watt chips that have been designed specifically for Chromebook usage. The current HX, HS and U suffix lettering will carry over, alongside the lower-case e for 9 W versions the U SKUs. AMD has also segmented it's mobile CPUs according to the chart below, to try and deliver a clearer use case for its various CPU models. The chart is pretty self explanatory, although some of the segmentation will apply to updated models of current designs, whereas others will only apply to new laptop designs. The new model numbering scheme will apply to at least 2025.