Wednesday, September 7th 2011

MSI Calls Bluff on Gigabyte's PCIe Gen 3 Ready Claim

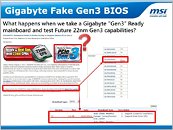

In August, Gigabyte made a claim that baffled at least MSI, that scores of its motherboards are Ready for Native PCIe Gen. 3. Along with the likes of ASRock, MSI was one of the first with motherboards featuring PCI-Express 3.0 slots, the company took the pains to educate buyers what PCI-E 3.0 is, and how to spot a motherboard that features it. MSI thinks that Gigabyte made a factual blunder bordering misinformation by claiming that as many as 40 of its motherboards are "Ready for Native PCIe Gen. 3." MSI decided to put its engineering and PR team to build a technically-sound presentation rebutting Gigabyte's claims.More slides, details follow.

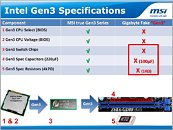

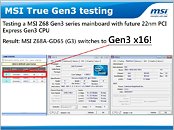

MSI begins by explaining that PCIe support isn't as easy as laying a wire between the CPU and the slot. It needs specifications-compliant lane switches and electrical components, and that you can't count on certain Gigabytes for future-proofing.MSI did some PCI-Express electrical testing using a 22 nm Ivy Bridge processor sample.MSI claims that apart from the G1.Sniper 2, none of Gigabyte's so-called "Ready for Native PCIe Gen. 3" motherboards are what the badge claims to be, and that the badge is extremely misleading to buyers. Time to refill the popcorn bowl.

Source:

MSI

MSI begins by explaining that PCIe support isn't as easy as laying a wire between the CPU and the slot. It needs specifications-compliant lane switches and electrical components, and that you can't count on certain Gigabytes for future-proofing.MSI did some PCI-Express electrical testing using a 22 nm Ivy Bridge processor sample.MSI claims that apart from the G1.Sniper 2, none of Gigabyte's so-called "Ready for Native PCIe Gen. 3" motherboards are what the badge claims to be, and that the badge is extremely misleading to buyers. Time to refill the popcorn bowl.

286 Comments on MSI Calls Bluff on Gigabyte's PCIe Gen 3 Ready Claim

You can't just expect a 5 GT/s circuitry to handle 8GT/s data without issues.I fail to see how you can not do a complete ROM reflash on any mainboard and require a dual bios for this since it's pretty much standard business in the server world.

Unless of course, one certain company that likes to promote dual bios'es on their boards would tell the press that "it might" and "it could" to make people afraid.Yes, or a simple Gen3 card with test chip.

For multi gpu yes you need PCIe3 switches for the bridge but Gigabyte have given all there 6 series pci gen3 for the first slot at least.

shame on you gigabyte ... would expected it to be asus

Otherwise it's impossible to switch the first slot between x16 and x8.

Right the pcie controller is on the cpu do you agree?

So if the controller is on the cpu and the traces are identical (They are) then why wont a single graphics card work at 16x gen3?

The switch is only used one a 2nd gpu is inserted

On top the CPU

8 PCIe lanes go the the first slot

8 PCIe lanes go the the 4 PCI express switches

If no card is detected in the second slot, all traffic will go to slot 1

The clock gen for the second PCIe card is actually housed in the PCH/southbridge

The only way to do 8/8 is by having switches and a setup like in the picture below

NO switches, IE all 16 lines are going straight from the CPU to the first slot results in 16/4 setups for crossfire for instance.

PCI-E 2.X is 5GT/s, but with the overhead, it is actually closer to 4GT/s, so 16 lanes of 2.X should be equivalent to 8 lanes of PCI-E 3.0 no?

This is what i said from the beginning

TBH, I'm not sure, exactly, what will happen with these boards and the primary slot. It's not as simple as it seems.

I've highlighted it on a gigabyte board so you can see where the lanes are coming from.

How to calculate PCI Express bandwidth:

Transfer rate * encoding

PCI Express Gen2:

Transfer rate: 5GT/s = 5000 Gb/s = 625 GB/s

625 * 8/10 (encoding) = 500 MB/s

PCI Express = Full duplex, so total bandwidth = 500*2 = 1GB/s

16 lanes*1GB/s = 16GB/s

PCI Express Gen3:

Transfer rate: 8GT/s = 8000Gb/s = 1000 GB/s

1000 * 128/130 = 984.6154 GB/s

PCI Express = Full Duplex, so total bandwidth = 984.6154 * 2 = 1969.2308

8 lanes *1969.2308GB/s = 15753.8464 GB/sNo, PLEASE, check the picture:

You can see that only 8 lanes are connected to the CPU (on top) the other 8 lanes come from the PCI express switches.

If you have a good high res picture of a board you can actually SEE the traces from the switch to the slot.

Please prove me wrong because I hate it when I make big mistakes in public :)

If you can show me a pericom switch that has a supersecret awesomemode where it magically transforms from a 5GT/s switch to a 8GT/s passive transceiver, you've got me convinced.

Otherwise, I have NO idea where you get your information from that the Gen2 switches can turn themselves of and do some mystical rerouting.Gigabyte's wording was "Gen3 maximum bandwidth" which would be 32GB/s not 16GB/s