Thursday, August 31st 2017

AMD Ryzen Threadripper 1900X Core Configuration Detailed

At its pre-launch media conference call for the Ryzen Threadripper 1900X, AMD mentioned that the chip has been carved out from the common 4-die EPYC MCM using a "4-0-4-0 diagonal configuration," which led to some confusion as to which cores/dies AMD disabled to carve out the $549 8-core HEDT processor. The company shed some light on this matter, responding to questions from TechPowerUp.

It turns out, that the Threadripper 1900X features an entire CCX (quad-core CPU complex) disabled per active die on the multi-chip module, so the CCX that's enabled has 8 MB of L3 cache; and access to the die's entire uncore resources, such as the dual-channel memory controller, PCIe root complex, etc. With two such active "Zeppelin" dies, the Threadripper 1900X ends up with 8 cores, 16 MB of L3 cache, a quad-channel memory interface, and 64 PCIe lanes.The decision to disable an entire CCX, rather than doing something similar to the "Zeppelin" die as with the Ryzen 5 1400, where both CCX units on the die are enabled with 2 cores, each; and the L3 cache per CCX being chopped down to 4 MB; could be attributed to giving the four cores per active CCX a contiguous block of 8 MB L3 cache, to better cushion the NUMA local mode, in which certain applications' memory access can be localized to one die, for lower latency.

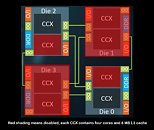

When AMD talks about a "diagonal configuration," it refers to the fact that two out of four 8-core "Zeppelin" dies physically present on the Threadripper multi-chip module, are disabled. The ones disabled are always diagonally opposite to each other. The Threadripper MCM is physically identical to the 32-core EPYC MCM, with four 8-core "Zeppelin" dies under its large integrated heatspreader (IHS); but due to platform-segmentation, and the fact that the Threadripper socket TR4 HEDT platform only has 4 memory channels (unlike 8 channels on the EPYC platform); two dies are completely disabled. The dies are disabled diagonally probably to spread heat better, or for better package wiring.

It turns out, that the Threadripper 1900X features an entire CCX (quad-core CPU complex) disabled per active die on the multi-chip module, so the CCX that's enabled has 8 MB of L3 cache; and access to the die's entire uncore resources, such as the dual-channel memory controller, PCIe root complex, etc. With two such active "Zeppelin" dies, the Threadripper 1900X ends up with 8 cores, 16 MB of L3 cache, a quad-channel memory interface, and 64 PCIe lanes.The decision to disable an entire CCX, rather than doing something similar to the "Zeppelin" die as with the Ryzen 5 1400, where both CCX units on the die are enabled with 2 cores, each; and the L3 cache per CCX being chopped down to 4 MB; could be attributed to giving the four cores per active CCX a contiguous block of 8 MB L3 cache, to better cushion the NUMA local mode, in which certain applications' memory access can be localized to one die, for lower latency.

When AMD talks about a "diagonal configuration," it refers to the fact that two out of four 8-core "Zeppelin" dies physically present on the Threadripper multi-chip module, are disabled. The ones disabled are always diagonally opposite to each other. The Threadripper MCM is physically identical to the 32-core EPYC MCM, with four 8-core "Zeppelin" dies under its large integrated heatspreader (IHS); but due to platform-segmentation, and the fact that the Threadripper socket TR4 HEDT platform only has 4 memory channels (unlike 8 channels on the EPYC platform); two dies are completely disabled. The dies are disabled diagonally probably to spread heat better, or for better package wiring.

63 Comments on AMD Ryzen Threadripper 1900X Core Configuration Detailed

I'm sure that by the end of Monday, the glorious TPU will write a retraction.

Just like in the old times. :D

My last new system was in 2009 when Intel were still soldering heat spreaders. It included (bleeding edge) 4x64GB OCZ Core in a raid 0 array. It cost me ~$6k (AUD). It would easily continue to serve (but for the failure of the array ... failed ssd). The speed lent to the cpu by the bootable raid 0 array (only achieving ~480MB/s) was a marvel to me at the time.

I would like to replace my current system (peripheral speeds being the main driver).

The chipset functionality that AMD has made available is very good for my preferences (and at least no worse than ~Z270-WS, which I have been considering, with possible exception of Thunderbolt 3.0).

I will happily be spending $4k-$5k (AUD) early next year on an AMD 1900x / Asus X399 Zenith Extreme system at about May 2018 (my current system's 9th birthday). I am likely to invest in GTX1050 Ti and Dell U2718Q (this may vary depending on what is available then). All storage will be ssd (probably M.2 and PCIE), this is the slowest part of the system and the changes will eliminate the slow transfers (300GB directories of files replacing archives etc) with current standards.

Thinking about the future and how that might change things I expect that the recognition of the importance of multithreading by developers will be a trend (where possible, perhaps not so, much in gaming)

I plan that the system I buy will meet my needs for 15 years. My preferences might best be summarised as:

Processor speed to be no worse / better than the current system (Nehalem core i7 965),

All slow parts of the system eliminated (transfer via USB / SATA, backups), and a

Better visual experience within the limit of visual acuity (20/20 = 177ppi @ 20').

Rgds

Time will figure that out, but I don't see them going back to the days of tri-core designs and such.