Monday, January 11th 2021

Dual-CCD Ryzen 5 5600X and Ryzen 7 5800X In the Wild

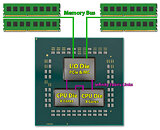

Certain AMD Ryzen 5 5600X and Ryzen 7 5800X processors are physically based on a dual-CCD design, according to an investigative report by Igor's Lab and Yuri "1usmus" Bubliy. The 5600X and 5800X are normally meant to be single-CCD processors owing to their core-counts. Based on the "Vermeer" multi-chip module design, the Ryzen 5000 series desktop processors use up to two 8-core CCDs to achieve their core-counts of up to 16 cores, with the 6-core 5600X and 8-core 5800X normally having just one CCD; while the 12-core 5900X and 16-core 5950X use two.

There are, apparently, some 5600X and 5800X built from dual-CCD MCMs, in which an entire CCD, although physically present on the package, is disabled. A 5600X based on a dual-CCD design is essentially a 5900X from which one of the CCDs didn't fully qualify; while the 5800X dual-CCD is a 5950X in which one such die didn't quite make the cut. There's no telling which CCD is disabled, it could be CCD 0 or CCD 1, those with CCD 0 disabled could trigger minor (benign) UI bugs with certain tuning utilities, which is how Wallossek and Bubliy discovered these chips. In any case, you're getting a 5600X or 5800X that works as advertised, and is fully covered by AMD's product warranties. Igor's Lab is investigating further into these dual-CCD 5600X and 5800X chips, and is probing the possibility of unlocking them to Ryzen 9.

Source:

Igor's Lab

There are, apparently, some 5600X and 5800X built from dual-CCD MCMs, in which an entire CCD, although physically present on the package, is disabled. A 5600X based on a dual-CCD design is essentially a 5900X from which one of the CCDs didn't fully qualify; while the 5800X dual-CCD is a 5950X in which one such die didn't quite make the cut. There's no telling which CCD is disabled, it could be CCD 0 or CCD 1, those with CCD 0 disabled could trigger minor (benign) UI bugs with certain tuning utilities, which is how Wallossek and Bubliy discovered these chips. In any case, you're getting a 5600X or 5800X that works as advertised, and is fully covered by AMD's product warranties. Igor's Lab is investigating further into these dual-CCD 5600X and 5800X chips, and is probing the possibility of unlocking them to Ryzen 9.

62 Comments on Dual-CCD Ryzen 5 5600X and Ryzen 7 5800X In the Wild

Inclusive vs. exclusive describes the relation between various levels of cache, not between parts of L3 that reside on separate dies, so it shouldn't matter here.

This is how a core-to-core latency measurement is done, I suppose:

1. A thread running on core A writes some data to memory location X

2. A thread running on core B reads data from memory location X a couple nanoseconds later

3. The control program measures how long core B has waited before it got the data

4. Everything is repeated many times to make sure all write buffers are overflown etc. At the end, some statistical calculations are performed.

Now if A and B are on separate dies, X needs to be copied from A's caches to B's caches (L3 may not even be involved here). To do this, it't not absolutely necessary to write X back to DRAM; however, that's what a Ryzen with two CCDs does, and that makes core-to-core latency as high as DRAM latency. This sounds bad but it probably allows the cache sync logic to be less complex and faster.

Some more info is here (for Ryzen 1), the most interesting bit is "This means that the true LLC for the entire chip is actually DRAM".

As for the above, I don't think your reasoning towards the end is right - that still feels like that would add far more latency than just DRAM latency, as there are more steps involved in a core-to-core measurement than in a straight DRAM access. The part of the sentence from the 1800X review also supports this, by saying that the two CCXes can communicate (implied: directly) through IF, bypassing memory. It's clear that cores on the same CCX can access each other through the L3, so I would assume the access pattern for intra-CCX access to be something like core-L3-IF-[some sort of management system on the IOD]-IF-L3-core.

But I entirely agree on your first point, I hope someone with greater knowledge could jump in and explain this to us :)

and tell you if ya gotta "decent" overclocker or not on the core side of things.

my 5600x is a 80 sil quality lowest ive seen out of 100s of other users using it. but

i can run 4000 1:1:1 DAILY c16 flat tuned without issues, overclocking a static core clock however

could only run 4600 at 1.35v and that wasnt prime stable. (did get CO dialed in tho)

this is that tool tho, drive.google.com/file/d/1p3ilWHGaVd_Afso4KqpjSsAVpfq88M85/view?usp=sharing

now my 5800x i get 5000 WHEA-19s an hour or did, now i get around 500 an hour with some IOD, CCD adjusting.

but its got 120 sil quality and hits 5ghz on most cores no issues.

none the less ill possibly just shut the dam logger up with Mannaitx's WHEA suppressor from OCN.

but yea its been stated that it can happen by a few who knows what theyre speaking on. not 100% sure or not.

but its being worked on ;)

I apparently have a Dual CCD 5600X.

Wondering if I should try the lottery again, or just go with a 5900X or wait for Zen4 launch.

It still OC's to 4.85GHz with AutoOC/Curve Optimizer enabled w/ -30 per core and 200 boost. But it is warm at that speed. lol.