8

Cores

8

Threads

70 W

TDP

1200 MHz

Frequency

2.5 GHz

Boost

CHA

Codename

VIA Socket 2084

Socket

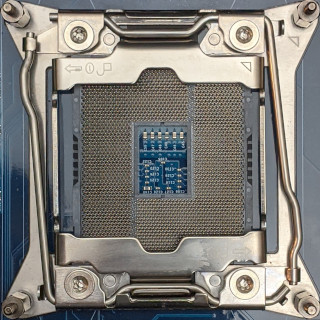

The VIA Centaur CHA was a server/workstation processor with 8 cores, that was never released. It is part of the CHA lineup, using the CNS architecture with VIA Socket 2084. To further increase overall system performance, up to two Centaur CHA CPUs can link up in a multi-processor (SMP) configuration. Centaur CHA has 16 MB of L3 cache and operates at 1200 MHz by default, but can boost up to 2.5 GHz, depending on the workload. VIA is building the Centaur CHA on a 16 nm production process, the transistor count is unknown. The silicon die of the chip is not fabricated at VIA, but at the foundry of TSMC. You may freely adjust the unlocked multiplier on Centaur CHA, which simplifies overclocking greatly, as you can easily dial in any overclocking frequency.

With a TDP of 70 W, the Centaur CHA consumes typical power levels for a modern PC. VIA's processor supports DDR4 memory with a quad-channel interface. The highest officially supported memory speed is 3200 MT/s, but with overclocking (and the right memory modules) you can go even higher. ECC memory is supported, too, which is an important capability for mission-critical systems, to avoid data corruption. For communication with other components in the system, Centaur CHA uses a PCI-Express Gen 3 connection. This processor lacks integrated graphics, you might need a graphics card.

Programs using Advanced Vector Extensions (AVX) will run on this processor, boosting performance for calculation-heavy applications. Besides AVX, VIA has added support for the newer AVX2 and AVX-512 instructions, too.

With a TDP of 70 W, the Centaur CHA consumes typical power levels for a modern PC. VIA's processor supports DDR4 memory with a quad-channel interface. The highest officially supported memory speed is 3200 MT/s, but with overclocking (and the right memory modules) you can go even higher. ECC memory is supported, too, which is an important capability for mission-critical systems, to avoid data corruption. For communication with other components in the system, Centaur CHA uses a PCI-Express Gen 3 connection. This processor lacks integrated graphics, you might need a graphics card.

Programs using Advanced Vector Extensions (AVX) will run on this processor, boosting performance for calculation-heavy applications. Besides AVX, VIA has added support for the newer AVX2 and AVX-512 instructions, too.

Physical

| Socket: | VIA Socket 2084 |

|---|---|

| Foundry: | TSMC |

| Process Size: | 16 nm |

| Die Size: | 195 mm² |

| Package: | FC-LGA2084 |

Processor

| Market: | Server/Workstation |

|---|---|

| Production Status: | End-of-life |

| Release Date: | Never Released |

| Intended Release: | 2H 2020 |

| Part#: | unknown |

Performance

| Frequency: | 1200 MHz |

|---|---|

| Turbo Clock: | up to 2.5 GHz |

| Base Clock: | 100 MHz |

| Multiplier: | 12.0x |

| Multiplier Unlocked: | Yes |

| Voltage: | 1.1 V |

| NCORE NPU: | up to 20.5 TOPS |

| TDP: | 70 W |

Architecture

| Codename: | CHA |

|---|---|

| Generation: |

CHA

(CNS) |

| Memory Support: | DDR4 |

| Rated Speed: | 3200 MT/s |

| Memory Bus: | Quad-channel |

| ECC Memory: | Yes |

| PCI-Express: |

Gen 3, 44 Lanes (CPU only) |

| Chipset: | Zhaoxin ZX-200 |

Core Config

| # of Cores: | 8 |

|---|---|

| # of Threads: | 8 |

| SMP # CPUs: | 2 |

| Integrated Graphics: | N/A |

Cache

| Cache L1: | 64 KB (per core) |

|---|---|

| Cache L2: | 256 KB (per core) |

| Cache L3: | 16 MB (shared) |

Features

|

Notes

| CHA SoC configuration combines eight CNS x86-64 cores with a 16-slice, 32,768-bit VLIW "NCORE" neural processing unit. |

Jul 1st, 2024 14:47 EDT

change timezone

Latest GPU Drivers

New Forum Posts

- The Official Thermal Interface Material thread (1267)

- PSU Warranty, yeah, What is it good for? (32)

- Bios Soyo rx580 8g (6)

- FFXIV Dawntrail has one of the worst stories in video game history. Literally makes no sense. 0/10 (14)

- does mobo limits choice of gpu? (11)

- 1000w XOC or Matrix flash to Suprim X 4090? (21)

- Lexar NQ710 (yes not NM710, NQ710) 2TB NAND Package (34)

- Windows 11 General Discussion (5196)

- What are you playing? (20960)

- upgrading GPU with 8-pins power connector (22)

Popular Reviews

- Endgame Gear OP1 8K Review

- Lian Li HydroShift LCD 360S AIO Review

- Corsair MP600 Mini 2 TB Review - Great Storage for Steam Deck

- XPG Invader X Review

- Upcoming Hardware Launches 2024 (Updated May 2024)

- XFX Radeon RX 7900 XTX Magnetic Air Review

- Bykski CPU-FIRE-ON-I CPU Water Block Review

- AMD Ryzen 7 7800X3D Review - The Best Gaming CPU

- ASUS GeForce RTX 4070 Super Dual Review

- Patriot Viper Xtreme 5 DDR5-7600 32 GB CL36 Review

Controversial News Posts

- AMD Outs Ryzen 5000XT Processors for Socket AM4, an 8-year Old Socket (208)

- Legendary Overclocker KINGPIN Leaves EVGA and Joins PNY to Develop Next-Generation GPUs for Extreme OC (195)

- AMD Says Ryzen 9000 Series Won't Beat 7000X3D Series at Gaming (140)

- Possible Specs of NVIDIA GeForce "Blackwell" GPU Lineup Leaked (139)

- First Reviews are Live and Snapdragon X Elite Doesn't Quite Deliver on Promised Performance (124)

- ASUS Enhances Customer Support Following Gamers Nexus Investigation (118)

- Nightmare Fuel for Intel: Arm CEO Predicts Arm will Take Over 50% Windows PC Market-share by 2029 (112)

- AMD to Revise Specs of Ryzen 7 9700X to Increase TDP to 120W, to Beat 7800X3D (102)