16

Cores

16

Threads

115 W

TDP

2.3 GHz

Frequency

3.2 GHz

Boost

Interlagos

Codename

Socket G34

Socket

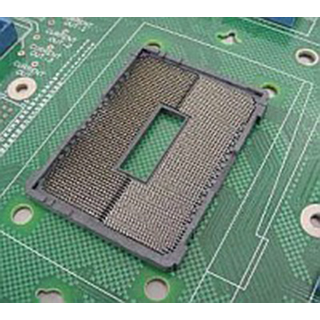

AMD Socket G34

The AMD Opteron 6276 was a server/workstation processor with 16 cores, launched in November 2011. It is part of the Opteron lineup, using the Interlagos architecture with Socket G34. To further increase overall system performance, up to four Opteron 6276 CPUs can work together in a multi-processor (SMP) configuration. Opteron 6276 has 8 MB of L3 cache per die and operates at 2.3 GHz by default, but can boost up to 3.2 GHz, depending on the workload. AMD is making the Opteron 6276 on a 32 nm production node using 2,400 million transistors. The multiplier is locked on Opteron 6276, which limits its overclocking potential.

With a TDP of 115 W, the Opteron 6276 consumes a lot of power, so good cooling is definitely needed. AMD's processor supports DDR3 memory. For communication with other components in the system, Opteron 6276 uses a PCI-Express Gen 2 connection. This processor lacks integrated graphics, you might need a graphics card.

Hardware virtualization is available on the Opteron 6276, which greatly improves virtual machine performance. Programs using Advanced Vector Extensions (AVX) can run on this processor, boosting performance for calculation-heavy applications.

With a TDP of 115 W, the Opteron 6276 consumes a lot of power, so good cooling is definitely needed. AMD's processor supports DDR3 memory. For communication with other components in the system, Opteron 6276 uses a PCI-Express Gen 2 connection. This processor lacks integrated graphics, you might need a graphics card.

Hardware virtualization is available on the Opteron 6276, which greatly improves virtual machine performance. Programs using Advanced Vector Extensions (AVX) can run on this processor, boosting performance for calculation-heavy applications.

Physical

| Socket: | AMD Socket G34 |

|---|---|

| Process Size: | 32 nm |

| Transistors: | 2,400 million |

| Die Size: | 316 mm² |

| Package: |

Processor

| Market: | Server/Workstation |

|---|---|

| Production Status: | End-of-life |

| Release Date: | Nov 14th, 2011 |

| Part#: | OS6276WKTGGGU |

Performance

| Frequency: | 2.3 GHz |

|---|---|

| Turbo Clock: | up to 3.2 GHz |

| Base Clock: | 200 MHz |

| Multiplier: | 11.5x |

| Multiplier Unlocked: | No |

| TDP: | 115 W |

Architecture

| Codename: | Interlagos |

|---|---|

| Generation: |

Opteron

(Interlagos) |

| Memory Support: | DDR3 |

| ECC Memory: | No |

| PCI-Express: | Gen 2 |

Core Config

| # of Cores: | 16 |

|---|---|

| # of Threads: | 16 |

| SMP # CPUs: | 4 |

| Integrated Graphics: | N/A |

Cache

| Cache L1: | 768 KB |

|---|---|

| Cache L2: | 16 MB |

| Cache L3: | 8 MB (per die) |

Features

|

Notes

| 16KB L1 data cache per core. 64KB L1 instruction cache shared per two cores (per module). 2MB L2 cache shared per two cores (per module). 8MB L3 cache shared per eight cores (per die). 14MB total L3 cache available when using HT Assist. |

Jul 16th, 2024 00:22 EDT

change timezone

Latest GPU Drivers

New Forum Posts

- External 8 TB SSDs before internal? (20)

- PC related hardware purchase that you regret very quickly after purchase. (164)

- WASD key lag in demanding games (Warzone, Dead Island 2, Fortnite) (6)

- What's your latest tech purchase? (21058)

- The Official Thermal Interface Material thread (1317)

- Very poor performance with Intel core i5-11600KF with stock 4.9 GHz (62)

- A Final Fantasy IX Reminiscence - My love letter and homage to one of the best stories ever told (23)

- ARC "driver issues" turning out to be actually hardware deficiencies - Battlemage reveal (37)

- How to fix performance issue (3)

- Sexy Hardware Close-Up Pic Clubhouse. (10256)

Popular Reviews

- AMD Zen 5 Technical Deep Dive

- HIFIMAN Susvara Unveiled Planar Magnetic Headphones Review

- Quick Look: Jelly Key Dragons of Eden Ethereal Runes Artisan Keycaps

- ID-Cooling FROZN A620 PRO SE Review - Better Value Than Thermalright

- HighPoint Rocket 1608A 8-Slot M.2 Gen 5 Review - 56 GB/s Transfer Rates

- The First Descendant Performance Benchmark Review - 30 GPUs Tested

- Upcoming Hardware Launches 2024 (Updated May 2024)

- AMD Ryzen 7 7800X3D Review - The Best Gaming CPU

- Corsair RS120 MAX 120 mm Fan Review

- XFX Radeon RX 7900 XTX Magnetic Air Review

Controversial News Posts

- Legendary Overclocker KINGPIN Leaves EVGA and Joins PNY to Develop Next-Generation GPUs for Extreme OC (195)

- Noctua Announces $150 Flagship NH-D15 G2 CPU Coolers and NF-A14x25r G2 140mm Fans (164)

- Microsoft Closer to Removing Local Accounts from Windows 11, Removes Help Page on How to Switch to One (142)

- AMD is Becoming a Software Company. Here's the Plan (139)

- NVIDIA GeForce RTX 50 Series "Blackwell" TDPs Leaked, All Powered by 16-Pin Connector (125)

- First Reviews are Live and Snapdragon X Elite Doesn't Quite Deliver on Promised Performance (124)

- AMD to Revise Specs of Ryzen 7 9700X to Increase TDP to 120W, to Beat 7800X3D (112)

- Intel "Arrow Lake-S" to See a Rearrangement of P-cores and E-cores Along the Ringbus (100)