Toshiba Develops New Bridge Chip Using PAM 4 to Boost SSD Speed and Capacity

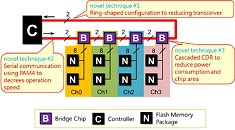

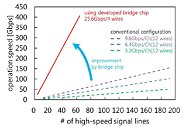

Toshiba Memory Corporation, the world leader in memory solutions, today announced the development of a bridge chip that realizes high-speed and large-capacity SSDs. Using developed bridge chips with a small occupied area and low-power consumption, the company has succeeded in connecting more flash memory chips with fewer high-speed signal lines than with the conventional method of no bridge chips. This result was announced in San Francisco on February 20, at the International Solid-State Circuits Conference 2019 (ISSCC 2019).

In SSDs, multiple flash memory chips are connected to a controller that manages their operation. As more flash memory chips are connected to a controller interface, operating speed degrades, so there are limits to the number of chips that can be connected. In order to increase capacity, it is necessary to increase the number of interfaces, but that results in an enormous number of high-speed signal lines connected to the controller, making it more difficult to implement the wiring on the SSD board.

In SSDs, multiple flash memory chips are connected to a controller that manages their operation. As more flash memory chips are connected to a controller interface, operating speed degrades, so there are limits to the number of chips that can be connected. In order to increase capacity, it is necessary to increase the number of interfaces, but that results in an enormous number of high-speed signal lines connected to the controller, making it more difficult to implement the wiring on the SSD board.