New AMD FirePro Deliver Unprecedented Levels of Performance for Mac Pro

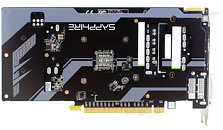

AMD announced dual AMD FirePro professional graphics solutions (GPUs) deliver unprecedented levels of performance for the new Mac Pro. The AMD FirePro D300, D500 and D700 professional GPUs offer exceptional compute power and reliability for creativity and productivity in a wide range of applications. With industry-adopted OpenCL (Open Computing Language) support, Mac Pro users have the ability to seamlessly edit full-resolution 4K video and simultaneously render effects in the background, and still have enough performance to power up to three high-resolution 4K displays.

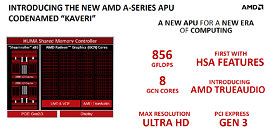

These new AMD FirePro GPUs are built on the strength of AMD's award-winning Graphics Core Next GPU design -- an architecture conceived from the ground up to intelligently manage rendering and compute workloads. The combination of AMD FirePro GPUs and OpenCL -- strongly supported by both Apple and AMD -- is designed to deliver massive compute and graphics performance in one compact solution.

These new AMD FirePro GPUs are built on the strength of AMD's award-winning Graphics Core Next GPU design -- an architecture conceived from the ground up to intelligently manage rendering and compute workloads. The combination of AMD FirePro GPUs and OpenCL -- strongly supported by both Apple and AMD -- is designed to deliver massive compute and graphics performance in one compact solution.