Mar 24th, 2025 10:22 EDT

change timezone

Latest GPU Drivers

New Forum Posts

- Black screen of death W11 (3)

- Do you prefer factory overclocked GPUs? (51)

- What are you playing? (23253)

- Is buying a PSU now a bad idea ? (4)

- UPS questions (54)

- Is RX 9070 VRAM temperature regular value or hotspot? (150)

- TPU's Nostalgic Hardware Club (20115)

- The TPU UK Clubhouse (25925)

- RTX 5080 worth it over 5070 TI for 4k? (23)

- TestMem5 broken? (9)

Popular Reviews

- Assassin's Creed Shadows Performance Benchmark Review - 30 GPUs Compared

- ASUS ProArt X870E-Creator Wi-Fi Review

- ASRock Radeon RX 9070 XT Taichi OC Review - Excellent Cooling

- ASUS GeForce RTX 5070 TUF OC Review

- Sapphire Radeon RX 9070 XT Nitro+ Review - Beating NVIDIA

- AMD Ryzen 9 9950X3D Review - Great for Gaming and Productivity

- Quick Look: Jelly Key Mystic Snake Artisan Keycaps

- MSI MAG B860 Tomahawk Wi-Fi Review

- AMD Ryzen 7 9800X3D Review - The Best Gaming Processor

- ASUS Radeon RX 9070 TUF OC Review

Controversial News Posts

- NVIDIA GeForce RTX 50 Cards Spotted with Missing ROPs, NVIDIA Confirms the Issue, Multiple Vendors Affected (519)

- AMD RDNA 4 and Radeon RX 9070 Series Unveiled: $549 & $599 (260)

- AMD Mentions Sub-$700 Pricing for Radeon RX 9070 GPU Series, Looks Like NV Minus $50 Again (250)

- AMD Radeon RX 9070-series Pricing Leaks Courtesy of MicroCenter (158)

- MSI Doesn't Plan Radeon RX 9000 Series GPUs, Skips AMD RDNA 4 Generation Entirely (142)

- Microsoft Introduces Copilot for Gaming (123)

- AMD Radeon RX 9070 XT Reportedly Outperforms RTX 5080 Through Undervolting (118)

- NVIDIA Reportedly Prepares GeForce RTX 5060 and RTX 5060 Ti Unveil Tomorrow (115)

News Posts matching #PCI-SIG

Return to Keyword BrowsingSD Express is a New Memory Card Standard That Leverages PCIe and NVMe

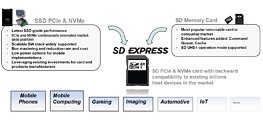

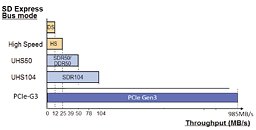

The SD Association announced today SD Express which adds the popular PCI Express and NVMe interfaces to the legacy SD interface. The PCIe interface delivering a 985 megabytes per second (MB/s) maximum data transfer rate and the NVMe upper layer protocol enables advanced memory access mechanism, enabling a new world of opportunities for the popular SD memory card. In addition, the maximum storage capacity in SD memory cards grows from 2 TB with SDXC to 128 TB with the new SD Ultra Capacity (SDUC) card. These innovations maintain the SDA's commitment to backward compatibility and are part of the new SD 7.0 specification.

"SD Express' use of popular PCIe and NVMe interfaces to deliver faster transfer speeds is a savvy choice since both protocols are widely used in the industry today and creates a compelling choice for devices of all types," said Mats Larsson, Senior Market Analyst at Futuresource. "The SD Association has a robust ecosystem with a strong history of integrating SD innovations and has earned the trust of consumers around the world."

"SD Express' use of popular PCIe and NVMe interfaces to deliver faster transfer speeds is a savvy choice since both protocols are widely used in the industry today and creates a compelling choice for devices of all types," said Mats Larsson, Senior Market Analyst at Futuresource. "The SD Association has a robust ecosystem with a strong history of integrating SD innovations and has earned the trust of consumers around the world."

AMD 400-series Chipset Surfaces on PCI-SIG, PCIe 3.0 General Purpose Confirmed

AMD's second-generation Ryzen processors, which debut some time in Q1-2018, will be accompanied by the company's new 400-series motherboard chipset, even though they are expected to work with existing socket AM4 motherboards based on 300-series chipsets (with BIOS updates). The 400-series Promontory chipset surfaced on the PCIe Integrators List of PCI-SIG, the standards governing body of the PCI bus (which also oversees PCIe specifications development).

The listing seems to confirm that 400-series chipset will feature PCI-Express gen 3.0 general purpose lanes. These are downstream PCIe lanes put out by the chipset, to run the various external onboard controllers on the motherboard, and usually wired to the x1 and x4 PCIe slots. The current 300-series chipset only features up to 8 PCIe gen 2.0 general purpose lanes, and that was seen as a drawback. AMD Ryzen socket AM4 processors put out additional gen 3.0 lanes besides the 16 lanes allocated to PEG (one x16 or two x8, physically x16 slots); and 4 lanes serving as chipset bus. These additional gen 3.0 lanes typically drive a 32 Gb/s M.2 slot. With 400-series chipset bringing gen 3.0 general purpose lanes, one can expect newer socket AM4 motherboards with more than one 32 Gb/s M.2 slot (one from the SoC, another from the chipset).

The listing seems to confirm that 400-series chipset will feature PCI-Express gen 3.0 general purpose lanes. These are downstream PCIe lanes put out by the chipset, to run the various external onboard controllers on the motherboard, and usually wired to the x1 and x4 PCIe slots. The current 300-series chipset only features up to 8 PCIe gen 2.0 general purpose lanes, and that was seen as a drawback. AMD Ryzen socket AM4 processors put out additional gen 3.0 lanes besides the 16 lanes allocated to PEG (one x16 or two x8, physically x16 slots); and 4 lanes serving as chipset bus. These additional gen 3.0 lanes typically drive a 32 Gb/s M.2 slot. With 400-series chipset bringing gen 3.0 general purpose lanes, one can expect newer socket AM4 motherboards with more than one 32 Gb/s M.2 slot (one from the SoC, another from the chipset).

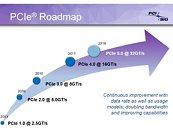

PCI-SIG: PCIe 4.0 in 2017, PCIe 5.0 in 2019

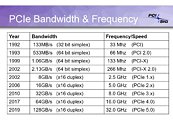

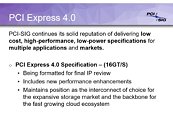

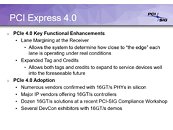

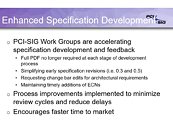

After years of continued innovation in PCIe's bandwidth, we've hit somewhat of a snag in recent times; after all, the PCIe 3.0 specification has been doing the rounds on our motherboards ever since 2010. PCI-SIG, the 750-member strong organization that's in charge of designing the specifications for the PCIe bus, attribute part of this delay to industry stagnation: PCIe 3.0 has simply been more than enough, bandwidth-wise, for many generations of hardware now. Only recently, with innovations in storage mediums and innovative memory solutions, such as NVMe SSDs and Intel's Optane, are we starting to hit the ceiling on what PCIe 3.0 offers. Add to that the increased workload and bandwidth requirements of the AI field, and the industry now seems to be eager for an upgrade, with some IP vendors even having put out PCIe 4.0-supporting controllers and PHYs into their next-generation products already - although at the incomplete 0.9 revision.

Mar 24th, 2025 10:22 EDT

change timezone

Latest GPU Drivers

New Forum Posts

- Black screen of death W11 (3)

- Do you prefer factory overclocked GPUs? (51)

- What are you playing? (23253)

- Is buying a PSU now a bad idea ? (4)

- UPS questions (54)

- Is RX 9070 VRAM temperature regular value or hotspot? (150)

- TPU's Nostalgic Hardware Club (20115)

- The TPU UK Clubhouse (25925)

- RTX 5080 worth it over 5070 TI for 4k? (23)

- TestMem5 broken? (9)

Popular Reviews

- Assassin's Creed Shadows Performance Benchmark Review - 30 GPUs Compared

- ASUS ProArt X870E-Creator Wi-Fi Review

- ASRock Radeon RX 9070 XT Taichi OC Review - Excellent Cooling

- ASUS GeForce RTX 5070 TUF OC Review

- Sapphire Radeon RX 9070 XT Nitro+ Review - Beating NVIDIA

- AMD Ryzen 9 9950X3D Review - Great for Gaming and Productivity

- Quick Look: Jelly Key Mystic Snake Artisan Keycaps

- MSI MAG B860 Tomahawk Wi-Fi Review

- AMD Ryzen 7 9800X3D Review - The Best Gaming Processor

- ASUS Radeon RX 9070 TUF OC Review

Controversial News Posts

- NVIDIA GeForce RTX 50 Cards Spotted with Missing ROPs, NVIDIA Confirms the Issue, Multiple Vendors Affected (519)

- AMD RDNA 4 and Radeon RX 9070 Series Unveiled: $549 & $599 (260)

- AMD Mentions Sub-$700 Pricing for Radeon RX 9070 GPU Series, Looks Like NV Minus $50 Again (250)

- AMD Radeon RX 9070-series Pricing Leaks Courtesy of MicroCenter (158)

- MSI Doesn't Plan Radeon RX 9000 Series GPUs, Skips AMD RDNA 4 Generation Entirely (142)

- Microsoft Introduces Copilot for Gaming (123)

- AMD Radeon RX 9070 XT Reportedly Outperforms RTX 5080 Through Undervolting (118)

- NVIDIA Reportedly Prepares GeForce RTX 5060 and RTX 5060 Ti Unveil Tomorrow (115)