Intel Launches Integrated Photonics Research Center

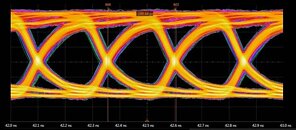

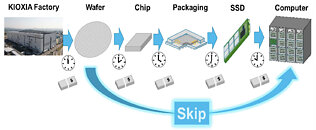

Intel Labs recently opened the Intel Research Center for Integrated Photonics for Data Center Interconnects. The center's mission is to accelerate optical input/output (I/O) technology innovation in performance scaling and integration with a specific focus on photonics technology and devices, CMOS circuits and link architecture, and package integration and fiber coupling.

"At Intel Labs, we're strong believers that no one organization can successfully turn all the requisite innovations into research reality. By collaborating with some of the top scientific minds from across the United States, Intel is opening the doors for the advancement of integrated photonics for the next generation of compute interconnect. We look forward to working closely with these researchers to explore how we can overcome impending performance barriers," said James Jaussi, senior principal engineer and director of the PHY Research Lab in Intel Labs.

"At Intel Labs, we're strong believers that no one organization can successfully turn all the requisite innovations into research reality. By collaborating with some of the top scientific minds from across the United States, Intel is opening the doors for the advancement of integrated photonics for the next generation of compute interconnect. We look forward to working closely with these researchers to explore how we can overcome impending performance barriers," said James Jaussi, senior principal engineer and director of the PHY Research Lab in Intel Labs.