Mar 28th, 2025 13:02 EDT

change timezone

Latest GPU Drivers

New Forum Posts

- 8 cores cpu (25)

- 4070tisuper (8)

- RTX 5080 worth it over 5070 TI for 4k? (56)

- Did Nvidia purposely gimp the performance of 50xx series cards with drivers (96)

- Future-proofing my OLED (37)

- Upgrade from a AMD AM3+ to AM4 or AM5 chipset MB running W10? (9)

- What is the most efficient way to clean up the OS after modifying hardware? (9)

- Application controll error 1000 rocket league (0)

- What's your latest tech purchase? (23420)

- TPU's Nostalgic Hardware Club (20137)

Popular Reviews

- Sapphire Radeon RX 9070 XT Pulse Review

- Samsung 9100 Pro 2 TB Review - The Best Gen 5 SSD

- Assassin's Creed Shadows Performance Benchmark Review - 30 GPUs Compared

- Pulsar Feinmann F01 Review

- ASRock Phantom Gaming B860I Lightning Wi-Fi Review

- be quiet! Pure Rock Pro 3 Black Review

- Sapphire Radeon RX 9070 XT Nitro+ Review - Beating NVIDIA

- ASRock Radeon RX 9070 XT Taichi OC Review - Excellent Cooling

- AMD Ryzen 7 9800X3D Review - The Best Gaming Processor

- AMD Ryzen 9 9950X3D Review - Great for Gaming and Productivity

Controversial News Posts

- MSI Doesn't Plan Radeon RX 9000 Series GPUs, Skips AMD RDNA 4 Generation Entirely (142)

- Microsoft Introduces Copilot for Gaming (123)

- AMD Radeon RX 9070 XT Reportedly Outperforms RTX 5080 Through Undervolting (118)

- NVIDIA Reportedly Prepares GeForce RTX 5060 and RTX 5060 Ti Unveil Tomorrow (115)

- Over 200,000 Sold Radeon RX 9070 and RX 9070 XT GPUs? AMD Says No Number was Given (100)

- NVIDIA GeForce RTX 5050, RTX 5060, and RTX 5060 Ti Specifications Leak (96)

- Retailers Anticipate Increased Radeon RX 9070 Series Prices, After Initial Shipments of "MSRP" Models (90)

- China Develops Domestic EUV Tool, ASML Monopoly in Trouble (88)

Monday, September 28th 2020

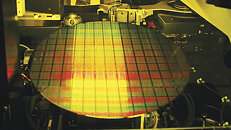

TSMC Ramps Up 3 nm Node Production

TSMC has had quite a good time recently. They are having all of their capacity fully booked and the development of new semiconductor nodes is going good. Today, thanks to the report of DigiTimes, we have found out that TSMC is ramping up the production lines to prepare for 3 nm high-volume manufacturing. The 3 nm node is expected to enter HVM in 2022, which is not that far away. In the beginning, the new node is going to be manufactured on 55.000 wafers of 300 mm size, and it is expected to reach as much as 100.000 wafers per month output by 2023. With the accelerated purchase of EUV machines, TSMC already has all of the equipment required for the manufacturing of the latest node. We are waiting to see more details on the 3 nm node as we approach its official release.

Source:

DigiTimes

Mar 28th, 2025 13:02 EDT

change timezone

Latest GPU Drivers

New Forum Posts

- 8 cores cpu (25)

- 4070tisuper (8)

- RTX 5080 worth it over 5070 TI for 4k? (56)

- Did Nvidia purposely gimp the performance of 50xx series cards with drivers (96)

- Future-proofing my OLED (37)

- Upgrade from a AMD AM3+ to AM4 or AM5 chipset MB running W10? (9)

- What is the most efficient way to clean up the OS after modifying hardware? (9)

- Application controll error 1000 rocket league (0)

- What's your latest tech purchase? (23420)

- TPU's Nostalgic Hardware Club (20137)

Popular Reviews

- Sapphire Radeon RX 9070 XT Pulse Review

- Samsung 9100 Pro 2 TB Review - The Best Gen 5 SSD

- Assassin's Creed Shadows Performance Benchmark Review - 30 GPUs Compared

- Pulsar Feinmann F01 Review

- ASRock Phantom Gaming B860I Lightning Wi-Fi Review

- be quiet! Pure Rock Pro 3 Black Review

- Sapphire Radeon RX 9070 XT Nitro+ Review - Beating NVIDIA

- ASRock Radeon RX 9070 XT Taichi OC Review - Excellent Cooling

- AMD Ryzen 7 9800X3D Review - The Best Gaming Processor

- AMD Ryzen 9 9950X3D Review - Great for Gaming and Productivity

Controversial News Posts

- MSI Doesn't Plan Radeon RX 9000 Series GPUs, Skips AMD RDNA 4 Generation Entirely (142)

- Microsoft Introduces Copilot for Gaming (123)

- AMD Radeon RX 9070 XT Reportedly Outperforms RTX 5080 Through Undervolting (118)

- NVIDIA Reportedly Prepares GeForce RTX 5060 and RTX 5060 Ti Unveil Tomorrow (115)

- Over 200,000 Sold Radeon RX 9070 and RX 9070 XT GPUs? AMD Says No Number was Given (100)

- NVIDIA GeForce RTX 5050, RTX 5060, and RTX 5060 Ti Specifications Leak (96)

- Retailers Anticipate Increased Radeon RX 9070 Series Prices, After Initial Shipments of "MSRP" Models (90)

- China Develops Domestic EUV Tool, ASML Monopoly in Trouble (88)

18 Comments on TSMC Ramps Up 3 nm Node Production

We are still way off real 3nm so the future aren't that scary yet :)

In late 2018, TSMC chairman Mark Liu predicted chip scaling would continue to 3 nm and 2 nm nodes; however, as of 2019 other semiconductor specialists were undecided as to whether nodes beyond 3 nm could become viable. TSMC began research on 2 nm in 2019. TSMC expected to transition from FinFET to GAAFET transistor types when moving from 3nm to 2nm. It has been reported that TSMC is expected to enter 2 nm risk production around 2023 or 2024. In Aug 2020 TSMC began building a R&D lab for 2nm technology in Hsinchu, expected to become partially operational by 2021. In Sep 2020 (SEMICOM Taiwan 2020) it was reported that TSMC Chairman Mark Liu had stated the company would build a plant for the 2nm node at Hsinchu in Taiwan, and that it could also install production at Taichung dependent on demand.

Intel's 2019 roadmap scheduled potentially equivalent 3nm and 2nm nodes for 2025 and 2027 respectively.

From there the industry moves to Angstrom as a measurement. Moore's Law will probably result in no law ... lawlessness, and trillionaire robber barons who own everything and every one and do whatever they like.

Intel 14 nm Node Compared to TSMC's 7 nm Node Using Scanning Electron Microscope

Also 3D chips, unsure if thats possible?

Oh and btw, GO TSMC !!!!!!!

Fabs give chip designers a library of cells and these cells usually are distinguished by their drive strength (size) and how much leakage that cell has.

Intel 14nm is 24nm by 24nm

TSMC 7nm is 22nm by 22nm

Curious eh?

Look for comment #41 made by RandallFlagg.

Transistor Gate Pitch seems not entirely related to the nm lithography process. What appears to be the new standard is Transistor density (MTr/mm^2).

The above table copied from the abovementioned post. I also recommend the following:

en.wikichip.org/wiki/7_nm_lithography_process