Intel Drops Xe-HP Server GPU Plans, to Stick with HPC and Client Graphics

Intel has dropped plans to build Xe-HP server GPUs commercially. This line of products would have powered cloud-based graphics rendering instances, for cloud-gaming or cloud-rendering applications. An announcement to this effect came from Raja Koduri, overseeing the development and monetization of Xe. Koduri stated that Xe-HP based instances were originally set up to power Intel's oneAPI devcloud as a software development vehicle for oneAPI and the upcoming Aurora supercomputer of the Argonne National Laboratory.

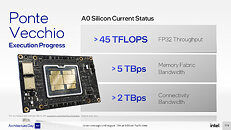

The company will now focus on Xe as a compute accelerator in the form of Xe-HPC "Ponte Vecchio," and discrete graphics in the client segment, leveraging the Xe-HPG graphics architecture. The smallest derivatives, the Xe-LP, powers integrated graphics solutions found in the company's Core processors (11th Gen and later). Back in the August 2021 Architecture Day presentation, Intel's technical brief for Xe HPC revealed that the silicon itself features certain on-die hardware relevant to graphics rendering (more here). This would have gone on to power the Xe-HP server GPU solutions.

The company will now focus on Xe as a compute accelerator in the form of Xe-HPC "Ponte Vecchio," and discrete graphics in the client segment, leveraging the Xe-HPG graphics architecture. The smallest derivatives, the Xe-LP, powers integrated graphics solutions found in the company's Core processors (11th Gen and later). Back in the August 2021 Architecture Day presentation, Intel's technical brief for Xe HPC revealed that the silicon itself features certain on-die hardware relevant to graphics rendering (more here). This would have gone on to power the Xe-HP server GPU solutions.