15

15

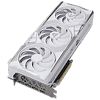

Colorful GeForce RTX 4070 Ti Super Vulcan W OC Review

Pictures & Teardown »Architecture

The Ada graphics architecture heralds the third generation of the NVIDIA RTX technology, an effort toward increasing the realism of game visuals by leveraging real-time ray tracing, without the enormous amount of compute power required to draw purely ray-traced 3D graphics. This is done by blending conventional raster graphics with ray traced elements such as reflections, lighting, and global illumination, to name a few. The 3rd generation of RTX introduces the new higher IPC "Ada" CUDA core, 3rd generation RT core, 4th generation Tensor core, and the new Optical Flow Processor, a component that plays a key role in generating new frames without involving the GPU's main graphics rendering pipeline. The GeForce Ada graphics architecture driving the RTX 4070 Ti SUPER leverages the TSMC 5 nm EUV foundry process to increase transistor counts.The GeForce RTX 4070 Ti SUPER gets a significant memory sub-system uplift over the original RTX 4070 Ti, besides an increase in shaders and other on-die components. Since NVIDIA maxed out the AD104 to create the RTX 4070 Ti, the only way it could go about creating the RTX 4070 Ti SUPER is by tapping into the larger AD103 that powers the RTX 4080 and the upcoming RTX 4080 SUPER. The biggest perks of the switch to AD103 is its wider 256-bit memory bus, which allowed NVIDIA to increase the memory from 12 GB to 16 GB.

The AD103 die is built on the 5 nm EUV foundry process, with a die size of 379 mm² and 45.9 billion transistors. The chip features a PCI-Express 4.0 x16 host interface along with support for PCI resizable BAR; and its 256-bit wide GDDR6X memory interface. The GigaThread Engine serves as the main workflow controller for the GPU, dispatching work among the GPU's 7 graphics processing clusters (GPCs). Each GPC shares a Raster Engine and render backends among six texture processing clusters (TPCs), the indivisible subunit of the GPU. Each of these has two Streaming Multiprocessors (SM), and a Polymorph unit. Each SM contains 128 CUDA cores across four partitions. Half of these CUDA cores are pure-FP32; while the other half is capable of FP32 or INT32. The SM retains concurrent FP32+INT32 math processing capability. The SM also contains a 3rd generation RT core, four 4th generation Tensor cores, some cache memory, and four TMUs. One of the seven GPCs on the AD103 physically only has four TPCs.

With a total of 40 TPCs, or 80 SM, AD103 physically features 10,240 CUDA cores, 320 Tensor cores, 80 RT cores, and 320 TMUs; along with 64 MB of on-die L2 cache, and 112 ROPs. NVIDIA carved the RTX 4070 Ti SUPER out of the AD103 by enabling 66 out of 80 SM, 48 MB out of the 64 MB of L2 cache present; and 96 ROPs out of the 112 present. This results in 8,448 CUDA cores, 264 Tensor cores, 66 RT cores, 264 TMUs, 96 ROPs, and 48 MB of L2 cache. NVIDIA also disabled a few NVDEC units, giving this the same exact video acceleration configuration as the RTX 4070 Ti, with two NVENC and one NVDEC units. The 256-bit memory interface drives 16 GB of memory, however the memory runs at 21 Gbps, compared to the 22.5 Gbps of the RTX 4080, and 23 Gbps of the upcoming RTX 4080 SUPER. Even with 21 Gbps, the memory bandwidth on tap is an impressive 672 GB/s, a 33% increase over that of the original RTX 4070 Ti.

3rd Gen RT Core and Ray Tracing

The 3rd generation RT core accelerates the most math-intensive aspects of real-time ray tracing, including BVH traversal. Displaced micro-mesh engine is a revolutionary feature introduced with the new 3rd generation RT core. Just as mesh shaders and tessellation have had a profound impact on improving performance with complex raster geometry, allowing game developers to significantly increase geometric complexity; DMMs is a method to reduce the complexity of the bounding-volume hierarchy (BVH) data-structure, which is used to determine where a ray hits geometry. Previously, the BVH had to capture even the smallest details to properly determine the intersection point. Ada's ray tracing architecture also receives a major performance uplift from Shader Execution Reordering (SER), a software-defined feature that requires awareness from game-engines, to help the GPU reorganize and optimize worker threads associated with ray tracing.

The BVH now needn't have data for every single triangle on an object, but can represent objects with complex geometry as a coarse mesh of base triangles, which greatly simplifies the BVH data structure. A simpler BVH means less memory consumed and helps to greatly reduce ray tracing CPU load, because the CPU only has to generate a smaller structure. With older "Ampere" and "Turing" RT cores, each triangle on an object had to be sampled at high overhead, so the RT core could precisely calculate ray intersection for each triangle. With Ada, the simpler BVH, plus the displacement maps can be sent to the RT core, which is now able to figure out the exact hit point on its own. NVIDIA has seen 11:1 to 28:1 compression in total triangle counts. This reduces BVH compile times by 7.6x to over 15x, in comparison to the older RT core; and reducing its storage footprint by anywhere between 6.5 to 20 times. DMMs could reduce disk- and memory bandwidth utilization, utilization of the PCIe bus, as well as reduce CPU utilization. NVIDIA worked with Simplygon and Adobe to add DMM support for their tool chains.

Opacity Micro Meshes

Opacity Micro Meshes (OMM) is a new feature introduced with Ada to improve rasterization performance, particularly with objects that have alpha (transparency data). Most low-priority objects in a 3D scene, such as leaves on a tree, are essentially rectangles with textures on the leaves where the transparency (alpha) creates the shape of the leaf. RT cores have a hard time intersecting rays with such objects, because they're not really in the shape that they appear (they're really just rectangles with textures that give you the illusion of shape). Previous-generation RT cores had to have multiple interactions with the rendering stage to figure out the shape of a transparent object, because they couldn't test for alpha by themselves.

This has been solved by using OMMs. Just as DMMs simplify geometry by creating meshes of micro-triangles; OMMs create meshes of rectangular textures that align with parts of the texture that aren't alpha, so the RT core has a better understanding of the geometry of the object, and can correctly calculate ray intersections. This has a significant performance impact on shading performance in non-RT applications, too. Practical applications of OMMs aren't just low-priority objects such as vegetation, but also smoke-sprites and localized fog. Traditionally there was a lot of overdraw for such effects, because they layered multiple textures on top of each other, that all had to be fully processed by the shaders. Now only the non-opaque pixels get executed—OMMs provide a 30 percent speedup with graphics buffer fill-rates, and a 10 percent impact on frame-rates.

DLSS 3 Frame Generation

DLSS 3 introduces a revolutionary new feature that promises a doubling in frame-rate at comparable quality, it's called AI frame-generation. Building on DLSS 2 and its AI super-resolution (scaling up a lower-resolution frame to native resolution with minimal quality loss); DLSS 3 can generate entire frames simply using AI, without involving the graphics rendering pipeline, it's also possible to enable frame generation at native resolution without upscaling. Later in the article, we will show you DLSS 3 in action.

Every alternating frame with DLSS 3 is hence AI-generated, without being a replica of the previous rendered frame. This is possible only on the Ada graphics architecture, because of a hardware component called the optical flow accelerator (OFA), which assists in predicting what the next frame could look like, by creating what NVIDIA calls an optical flow-field. OFA ensures that the DLSS 3 algorithm isn't confused by static objects in a rapidly-changing 3D scene (such as a race sim). The process heavily relies on the performance uplift introduced by the FP8 math format of the 4th generation Tensor core. A third key ingredient of DLSS 3 is Reflex. By reducing the rendering queue to zero, Reflex plays a vital role in ensuring that latency with DLSS 3 enabled is at an acceptable level. A combination of OFA and the 4th Gen Tensor core is why the Ada architecture is required to use DLSS 3, and why it won't work on older architectures.

Mar 27th, 2025 21:50 EDT

change timezone

Latest GPU Drivers

New Forum Posts

- How to quickly & easily fix coil-whine(coil choke noise) (1139)

- Post your CrystalDiskMark speeds (614)

- Gigabyte graphic card - TIM GEL application failure? (7)

- vram usage set (1)

- tape v hard disk (18)

- The TPU UK Clubhouse (25981)

- TPU's Nostalgic Hardware Club (20132)

- Fun with SBCs (7)

- Future-proofing my OLED (28)

- 9070 XT - 2x HDMI high refresh displays (144 and 120 Hz) not working (68)

Popular Reviews

- Sapphire Radeon RX 9070 XT Pulse Review

- Samsung 9100 Pro 2 TB Review - The Best Gen 5 SSD

- Assassin's Creed Shadows Performance Benchmark Review - 30 GPUs Compared

- Pulsar Feinmann F01 Review

- ASRock Phantom Gaming B860I Lightning Wi-Fi Review

- be quiet! Pure Rock Pro 3 Black Review

- Sapphire Radeon RX 9070 XT Nitro+ Review - Beating NVIDIA

- ASRock Radeon RX 9070 XT Taichi OC Review - Excellent Cooling

- ASUS ProArt X870E-Creator Wi-Fi Review

- Montech XR Wood Review

Controversial News Posts

- AMD RDNA 4 and Radeon RX 9070 Series Unveiled: $549 & $599 (260)

- MSI Doesn't Plan Radeon RX 9000 Series GPUs, Skips AMD RDNA 4 Generation Entirely (142)

- Microsoft Introduces Copilot for Gaming (123)

- AMD Radeon RX 9070 XT Reportedly Outperforms RTX 5080 Through Undervolting (118)

- NVIDIA Reportedly Prepares GeForce RTX 5060 and RTX 5060 Ti Unveil Tomorrow (115)

- Over 200,000 Sold Radeon RX 9070 and RX 9070 XT GPUs? AMD Says No Number was Given (100)

- NVIDIA GeForce RTX 5050, RTX 5060, and RTX 5060 Ti Specifications Leak (96)

- Retailers Anticipate Increased Radeon RX 9070 Series Prices, After Initial Shipments of "MSRP" Models (90)