Expect High-end Navi: AMD CEO

At a Q&A session with the tech press in Las Vegas, AMD CEO Dr Lisa Su raised hopes of a high-end graphics card based on its "Navi" family of GPUs. Responding to a specific question by Gordon Ung from PC World on whether there will be a high-end competitor in the discrete graphics space, Dr Su stated that one should expect a "high-end Navi." Dr Su states: "I know those on Reddit want a high end Navi! You should expect that we will have a high-end Navi, and that it is important to have it. The discrete graphics market, especially at the high end, is very important to us. So you should expect that we will have a high-end Navi, although I don't usually comment on unannounced products."

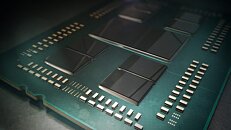

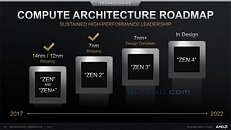

For months now, it's been speculated that AMD has been working on a larger GPU die than "Navi 10." In 2020, AMD is expected to release the "Navi 20" familly of GPUs built on 7 nm+ (EUV) node, based on the RDNA2 graphics architecture. The key design goals of RDNA2 are expected to be support for at least tier-1 variable-rate shading (VRS), and possibly hardware-accelerated ray-tracing. It's possible that "high-end Navi" belongs to this family of GPUs.

For months now, it's been speculated that AMD has been working on a larger GPU die than "Navi 10." In 2020, AMD is expected to release the "Navi 20" familly of GPUs built on 7 nm+ (EUV) node, based on the RDNA2 graphics architecture. The key design goals of RDNA2 are expected to be support for at least tier-1 variable-rate shading (VRS), and possibly hardware-accelerated ray-tracing. It's possible that "high-end Navi" belongs to this family of GPUs.