Monday, April 29th 2019

AMD X570 Chipset to Feature 40 PCIe 4.0 Lanes

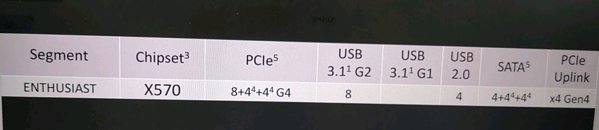

As we gear up for launch of AMD-s Ryzen 3000 series, details are bound to come up with increasing frequency. One of the latest, regarding AMD's in-house developed X570 chipset, which brings a renewed feature set to the AM4 platform, pertains to its PCIe lanes. AMD has included a grand total of 40 PCIe 4.0 lanes on the chipset, which will be distributed between PCIe uplink, USB 3.1 Gen2, USB 2.0 and SATA, as the spec sheet below (which may not be real) indicates. That's a whole load of bandwidth for the PC platform, not counting those PCIe lanes that are to be provided by the Ryzen CPUs.

It seems AMD will be using PCIe support level as a differentiator factor for its chipsets. The X570 is reported to be the only chipset to feature PCIe 4.0 support, while all other chipsets below it (B550 and so on) will only support PCIe 3.0. These lower-end chipsets should be manufactured by ASMedia.

Source:

Bilibili

It seems AMD will be using PCIe support level as a differentiator factor for its chipsets. The X570 is reported to be the only chipset to feature PCIe 4.0 support, while all other chipsets below it (B550 and so on) will only support PCIe 3.0. These lower-end chipsets should be manufactured by ASMedia.

27 Comments on AMD X570 Chipset to Feature 40 PCIe 4.0 Lanes

All I/O on chipset is discrete unlike Intel's chipset, thats means you cant convert USB to pcie lane.

"but some of these 40 channels are shared with the sata interface."

Why, just why?

And more over PCIe 4.0 ? Does that even bother to exist where most peripherals not even manage to provide significant or perhaps a dramatic change ? The only utilisation iv seen from PCIe 2 to gen 3 are nvme speeds which itself are hardly noticeable...

Correct me if im wrong...

It is more for marketing and bragging rights, 4 is bigger then 3. I don't see what curently will have benefit from it.

It's good to see AMD on the front foot with PCIe 4.0 with the 500 series chipset (albeit only the X570 variant).

First of all, the details in the leak appears to be correct from what I know and have known for several months and hinted at here before in other threads.

I don't know where the 40 PCIe lane rumour comes from, but unless you count the lanes in the CPU, it's not going to get anywhere close.

The chipset will have a significant amount of high-speed interfaces and if we use Intel naming, we can call it HSIO. I don't know if AMD will offer the same flexible IO as Intel does with its current PCH implementation, but it's a possibility. Even so, that doesn't make it 40 lanes.

The X570 chipset should be able to support at least two M.2 slots via the chipset and the new CPUs should still support a third M.2 slot that will be directly connected to the CPU, just as with the current Ryzen processors.

PCIe 4.0 SSDs are expected before the end of the year in retail. Expect early devices to be shown at Computex.

Technically the x16 slot from the CPU and the M.2 slot from the CPU when it comes to Ryzen 3000 parts (not counting the APUs), will support PCIe 4.0 on any board, as long as it has been designed to meet the speeds. Not all current boards will be capable of doing this, but some boards might be able to support PCIe 4.0 for those two ports. This also applies to a potential future B550 chipset.

Note that not all X570 boards will fully support PCIe 4.0 either, due to the cost of the PCIe 4.0 retimer/redriver/repeater whatever it is that is required to make PCIe 4.0 work. This will also depend on chipset placement on the boards and a few other things. PCIe 4.0 is apparently not that easy to design in on the ATX motherboard form factor, as the trace lengths easily get too long and the signal degrades. We might end up getting to see some interesting board layouts to try and make PCIe 4.0 work better, but judging by the presumed board picture from Biostar that has made the rounds, this might not be the case. Note that Biostar has covered up the picture on their site since then www.biostar.com.tw/app/en/news/news.php?S_ID=361

As AMD doesn't have an integrated Ethernet MAC in their chipsets, at least one PCIe lane will be used for Ethernet.So you mean exactly what Intel does with their PCH and DMI? Let's wait and see though, as there might be more to it than this leak details.

CPU - 16 (GPU) + 4 (NVMe) + 4 (downlink to chipset) = 24

Chipset (8+4+4) = 16 (of those 4+4 can be used to extend default 4 SATA config to 6 SATA config - just like in Ryzen 1xxx and 2xxx chipsets)

Together you get 40 lines. It's unfortunately like Intel marketing where they combine CPU and Chipset lines. Sad but true.

B550 according to original story do have PCIEx 4.0 - they are having some problems on some boards, but chipset as it is does have it implemented.