Monday, December 9th 2019

Centaur Releases In-Depth Analysis from The Linley Group for its NCORE-Equipped x86 Processor

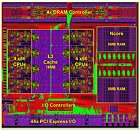

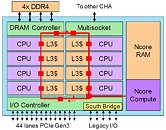

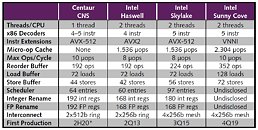

Centaur Technology today revealed in-depth information about its new processor-design technology for integrating high-performance x86 CPUs with a specialized co-processor optimized for artificial intelligence (AI) acceleration. On its website, Centaur provides a new independent report from The Linley Group, the industry's leading authority on microprocessor technology and publishers of Microprocessor Report. The Linley Group reviewed Centaur's detailed design documents and interviewed Centaur's CPU and AI architects to support the analysis of both Centaur's newest x86 microarchitecture and the AI co-processor design.

"Centaur is galloping back into the x86 market with an innovative processor design that combines eight high-performance CPUs with a custom deep-learning accelerator (DLA). The company is the first to announce a server-processor design that integrates a DLA. The new accelerator, called Ncore, delivers better neural-network performance than even the most powerful Xeon, but without the high cost of an external GPU card," stated Linley Gwennap, Editor-in-Chief, Microprocessor Report.The report can be accessed here (PDF).

The Linley Group referenced certified MLPerf benchmark (Preview) scores to compare Centaur's AI performance to high-end x86 CPU cores from the leading x86 vendor. Based on MLPerf scores, Centaur's AI-coprocessor inference performance is comparable to 23 of Intel's world-class x86 cores that now support 512-bit vector neural network instructions (VNNI). Centaur's AI co-processor uses an architecturally similar single-instruction-multiple-data (SIMD) approach as VNNI, but crunches 32,768 bits in a single clock cycle using a 16 MB memory with 20 terabytes/sec of bandwidth. Moreover, by offloading inference processing to a specialized co-processor, the x86 CPU cores remain available for other, more general-purpose tasks. Application developers can innovate new algorithms that take advantage of the unparalleled inference latency enabled by Centaur's AI performance and tight integration with x86 CPUs.

Attendees at the ISC East trade show in NYC saw Centaur's new technology up close for the first time. The demo showcased video analytics using Centaur's reference system with x86-based network-video-recording (NVR) software from Qvis Labs. In addition to conventional, real-time object detection/classification, Centaur was the only vendor at the show to highlight leading-edge applications such as semantic segmentation (pixel-level image classification) and a new technique for human pose estimation ("stick figures"). Centaur is focused on improving the hardware price/performance and software productivity for platforms to support this next wave of research applications and speed deployment into new server-class products.

"Centaur is galloping back into the x86 market with an innovative processor design that combines eight high-performance CPUs with a custom deep-learning accelerator (DLA). The company is the first to announce a server-processor design that integrates a DLA. The new accelerator, called Ncore, delivers better neural-network performance than even the most powerful Xeon, but without the high cost of an external GPU card," stated Linley Gwennap, Editor-in-Chief, Microprocessor Report.The report can be accessed here (PDF).

The Linley Group referenced certified MLPerf benchmark (Preview) scores to compare Centaur's AI performance to high-end x86 CPU cores from the leading x86 vendor. Based on MLPerf scores, Centaur's AI-coprocessor inference performance is comparable to 23 of Intel's world-class x86 cores that now support 512-bit vector neural network instructions (VNNI). Centaur's AI co-processor uses an architecturally similar single-instruction-multiple-data (SIMD) approach as VNNI, but crunches 32,768 bits in a single clock cycle using a 16 MB memory with 20 terabytes/sec of bandwidth. Moreover, by offloading inference processing to a specialized co-processor, the x86 CPU cores remain available for other, more general-purpose tasks. Application developers can innovate new algorithms that take advantage of the unparalleled inference latency enabled by Centaur's AI performance and tight integration with x86 CPUs.

Attendees at the ISC East trade show in NYC saw Centaur's new technology up close for the first time. The demo showcased video analytics using Centaur's reference system with x86-based network-video-recording (NVR) software from Qvis Labs. In addition to conventional, real-time object detection/classification, Centaur was the only vendor at the show to highlight leading-edge applications such as semantic segmentation (pixel-level image classification) and a new technique for human pose estimation ("stick figures"). Centaur is focused on improving the hardware price/performance and software productivity for platforms to support this next wave of research applications and speed deployment into new server-class products.

14 Comments on Centaur Releases In-Depth Analysis from The Linley Group for its NCORE-Equipped x86 Processor

In the end, I expect this to be a very poor client-desktop product. Its niche is the integrated wide SIMD core.

As you said there was no comment made from them on power or clock-speed headroom. With the right 10 nm class (12/14/16 FF) node, they might be able to come up with a client-segment product. If they've achieved single-thread parity with Zen+, then all they need is to sustain 3.80-4.00 GHz to torment current Core i5 chips. The only thing stopping this chip from hurting Pentium/Celeron/Core i3 is the lack of an iGPU. I doubt if VIA can pull off a contemporary iGPU today. So their embedded motherboards will have to bundle something like a GeForce MX150.

For the market this is currently aimed at, the only support needed would be basic delivery, initial implementation (API and documentation) and aftersales repair/replacement for any defects.

It's The Linley Group adding the PR, not VIA/Centaur themselves. They speculate that if this is priced the same as the Xeon Silver, they would be getting the accelerator for free, in a sense.