Friday, March 6th 2020

AMD "Zen 4" Microarchitecture On Track for 2021-22 Debut with "Genoa"

AMD's 4th generation EPYC line of enterprise processors, now into design stage, impressed the United States Department of Energy enough that it wants to deploy it in "El Capitan," a 2 ExaFLOP supercomputer that will be the world's most powerful, when it goes online around 2022. Codenamed "Genoa," 4th gen EPYC implements AMD's "Zen 4" microarchitecture. While AMD didn't get into too many details about it in its 2020 Financial Analyst Day address, there are a couple of details.

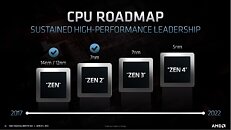

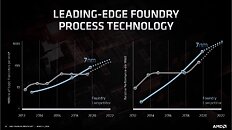

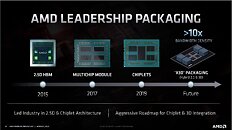

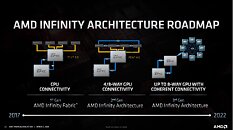

For starters, "Zen 4" continues on AMD's trajectory of adding IPC gains with each generation. Secondly, "Zen 4" will leverage the advanced 5 nm silicon fabrication process, which should significantly increase transistor densities over even the most advanced iterations of 7 nm, such as 7 nm EUV. "Zen 4" comes out roughly the same time as the RDNA3 and CDNA2 graphics architectures, and AMD's 3rd generation Infinity Fabric interconnect that enables exascale supercomputers thanks to coherent unified memory and vast shared memory pools between CPUs and compute GPUs. Elsewhere in the roadmap, we see AMD announcing that its upcoming "Zen 3" microarchitecture and its enterprise implementation, the EPYC "Milan" processor, will release only toward the end of 2020. This would give EPYC "Rome" close to 6 calendar quarters of market leadership.Although not in reference to "Genoa," AMD briefly talked about the next step in its package innovations that have helped it overcome the effects of a slowdown in Moore's Law cadence. The company implemented MCMs for its first-generation "Naples," and transcended to the chiplet approach with second generation "Rome," in which only those components that benefit from the switch to a new node would be built on the new node, while uncore and I/O components would be built on separate dies and older process nodes, which is largely expected to carry forward with "Milan." Some time in the future, through, the company could embrace an X3D "2.5D + 3D" package design that sees the combination of 3D memory stacks sitting alongside 2.5D logic stacks.

For starters, "Zen 4" continues on AMD's trajectory of adding IPC gains with each generation. Secondly, "Zen 4" will leverage the advanced 5 nm silicon fabrication process, which should significantly increase transistor densities over even the most advanced iterations of 7 nm, such as 7 nm EUV. "Zen 4" comes out roughly the same time as the RDNA3 and CDNA2 graphics architectures, and AMD's 3rd generation Infinity Fabric interconnect that enables exascale supercomputers thanks to coherent unified memory and vast shared memory pools between CPUs and compute GPUs. Elsewhere in the roadmap, we see AMD announcing that its upcoming "Zen 3" microarchitecture and its enterprise implementation, the EPYC "Milan" processor, will release only toward the end of 2020. This would give EPYC "Rome" close to 6 calendar quarters of market leadership.Although not in reference to "Genoa," AMD briefly talked about the next step in its package innovations that have helped it overcome the effects of a slowdown in Moore's Law cadence. The company implemented MCMs for its first-generation "Naples," and transcended to the chiplet approach with second generation "Rome," in which only those components that benefit from the switch to a new node would be built on the new node, while uncore and I/O components would be built on separate dies and older process nodes, which is largely expected to carry forward with "Milan." Some time in the future, through, the company could embrace an X3D "2.5D + 3D" package design that sees the combination of 3D memory stacks sitting alongside 2.5D logic stacks.

9 Comments on AMD "Zen 4" Microarchitecture On Track for 2021-22 Debut with "Genoa"

hmm. I'm half tempted to wait and build a balls to the wall zen 4 rig now. I know 100% I am buying playstation 5 on launch day, so I don't see any reason why I can't delay again. PS5 will keep me plenty busy until Fall/Winter 2021.

I wonder if the new 'IA' is full duplex, since it seems IF is limited to being half-duplex.

Though, if this means HBM on package that's cool.

Though ironically AMD's collaboration with Intel will be the first for that. :laugh:

The CCX will be 8-core, the chiplet will remain 8-core with 32+ MB L3 cache.

www.notebookcheck.net/Latest-Zen-3-rumor-further-reiterates-10-15-IPC-gains-per-thread-and-32-MB-of-shared-L3-cache-per-CCX-Zen-4-to-feature-1-MB-L2-cache-and-AVX-512-support.459845.0.html

ownsnap.com/amd-zen-3-desktop-processors-will-be-10-15-faster-than-zen-2-in-ipc-performance-have-8-core-per-ccx-with-unified-l3-cache/

I've never met her, boom boom, I'll let myself out. :p