Sunday, May 9th 2021

Rumor: AMD Rembrandt APUs to Feature Zen3+, RDNA2 Architectures - Up to 12 CUs

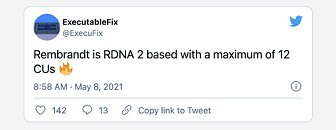

A fresh rumor straight from the rumor mill paints AMD's next APU iterations as being updated to the latest and greatest architectures the company has to offer. The rumor comes from ExecutableFix via Twitter, a leaker who has a relatively proven track record on being right regarding upcoming hardware releases. This rumor can lay some credence to others, painting AMD's Ryzen 7000 series as being the first AMD APU-only release since they began their journey with the Zen architecture - it makes sense for the company to integrate their latest architectures in the mobile-geared Rembrandt first, working out some possible interaction quirks that might arise between the two architectures when deployed in the same package.

The leaker further affirms that the Rembrandt APUs will feature up to 12 RDNA2 CUs, which would amount to 768 stream processors on-chip - a marked increase from the current-generation 8 CUs based on the Vega architecture on their Ryzen 4000 mobile series. The leaker also discloses that AMD's Warhol seems to be MIA in recent AMD documentation and planning when it comes to the deployment of Zen3+, and that Rembrandt should be the one to carry that particular architecture refinement through to the 6 nm process. It would seem that AMD's Vega would "finally" see its demise, bringing about some much-needed performance improvements to counter Intel's investments in GPU performance with Xe.

Sources:

ExecutableFix @ Twitter, via Videocardz

The leaker further affirms that the Rembrandt APUs will feature up to 12 RDNA2 CUs, which would amount to 768 stream processors on-chip - a marked increase from the current-generation 8 CUs based on the Vega architecture on their Ryzen 4000 mobile series. The leaker also discloses that AMD's Warhol seems to be MIA in recent AMD documentation and planning when it comes to the deployment of Zen3+, and that Rembrandt should be the one to carry that particular architecture refinement through to the 6 nm process. It would seem that AMD's Vega would "finally" see its demise, bringing about some much-needed performance improvements to counter Intel's investments in GPU performance with Xe.

31 Comments on Rumor: AMD Rembrandt APUs to Feature Zen3+, RDNA2 Architectures - Up to 12 CUs

The bad news is that it's a LOOOOONG way away and Intel's IGPs are improving much faster than AMD's IGPs are improving; It may be too little, too late.

Back to Zen3+, will it be AM4, AM5, or both? Given that AMD's using a chiplet design, in theory it wouldn't be too hard for them to make separate DDR4 and DDR5 I/O dies.

By the time Alder Lake arrives, AMD needs to have something new ready too. Without unlimited resources, they can't have a new socket, new chipset, new Zen, and new DDR and new PCIe controllers, all at the same time and properly tested. Without really unlimited resources, they can't steal 5nm wafer starts from under Apple's nose. So they decide on AM5 and DDR5, but old Zen (refreshed), old process (refreshed) and old PCIe, which is a good fit for a monolithic APU. The graphics will benefit a lot from DDR5 bandwidth here.

It will be something of a disappointment to enthusiasts, but so will be Alder Lake, so there. AMD then has enough time to finish Zen 4 and PCIe 5, and debug DDR5.

Regarding DDR5, there's surprisingly little information about it half a year before supposed launch, and the available info points at high latencies. I think that the technology is difficult like hell to implement and the first generation of controllers (from AMD, Intel, whoever) and modules will come loaded with bugs, with poor compatibility, stability and latencies. And gears, oh, gears! But you've got to start somewhere, and it better be a midrange product than something aimed at the most demanding crowd.