Monday, May 31st 2021

AMD "Zen 3+" Microarchitecture is "Zen 3" with 3D Vertical Cache Technology, 15% Gaming Perf Gain

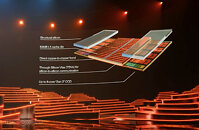

AMD CEO Dr Lisa Su, in her Computex 2021 Keynote address detailed what could very well be the "Zen 3+" microarchitecture that's been in the news lately, although the name "Zen 3+" was never used in the keynote address. AMD has collaborated with TSMC on developing a new die-on-die 3D stacking technology using TSVs (through-silicon vias) and structural silicon substrate, to place a 64 MB SRAM on top of the "Zen 3" CCD, which it calls 3D Vertical Cache. This cache die sits directly over the region that has the CCD's own 32 MB L3 cache, and the difference in height between the two dies is leveled using structural silicon. At this point we don't know how the cache hierarchy is changed, whether the 64 MB add-on cache is contiguous with the on-die L3 cache, or whether it's an L4 victim cache to the L3$. With it, the total cache amount of the CCD jumps to 100 MB (4 MB L2 caches + 32 MB L3 cache + 64 MB 3D Vertical Cache).

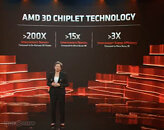

AMD has made some startling claims as to the performance impact of 3D Vertical Cache Technology. It claims that gaming performance improves by an average of 15%, which is akin to a generational performance impact in and of itself. With these gains, AMD hopes to make up whatever gaming performance deficit the "Zen 3" microarchitecture has against Intel's "Rocket Lake-S." The first processors implementing 3D Vertical Cache Technology will start arriving by the end of 2021, which means it could very well be the Ryzen 6000 series desktop processors, leaving the Ryzen 7000 series to be based on the 5 nm "Zen 4," on track to a 2022 release.How AMD plans to release these updated dies on the client ecosystem remains a mystery. The prototype Dr Su showed in her keynote address clearly appears to be Socket AM4. If the new Socket AM5 is on course to later this year, it's very likely that these "Zen 3 + 3D VC" CCDs could be paired with an updated cIOD (client I/O die) that supports DDR5 memory, and packaged for AM5.

AMD has made some startling claims as to the performance impact of 3D Vertical Cache Technology. It claims that gaming performance improves by an average of 15%, which is akin to a generational performance impact in and of itself. With these gains, AMD hopes to make up whatever gaming performance deficit the "Zen 3" microarchitecture has against Intel's "Rocket Lake-S." The first processors implementing 3D Vertical Cache Technology will start arriving by the end of 2021, which means it could very well be the Ryzen 6000 series desktop processors, leaving the Ryzen 7000 series to be based on the 5 nm "Zen 4," on track to a 2022 release.How AMD plans to release these updated dies on the client ecosystem remains a mystery. The prototype Dr Su showed in her keynote address clearly appears to be Socket AM4. If the new Socket AM5 is on course to later this year, it's very likely that these "Zen 3 + 3D VC" CCDs could be paired with an updated cIOD (client I/O die) that supports DDR5 memory, and packaged for AM5.

56 Comments on AMD "Zen 3+" Microarchitecture is "Zen 3" with 3D Vertical Cache Technology, 15% Gaming Perf Gain

And it makes sense that even if Zen 3+ is great, Zen 4 will be even better.