AMD FX-8350 Pushed to 8.1 GHz via Extreme Overclocking by Der8auer

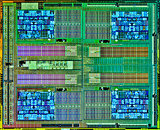

AMD's Bulldozer architecture is a well-known quantity by now, and seemingly straddles a line between loathing and love between tech enthusiasts. Slow and power hungry compared to Intel's options, it harkens back to a time where the roles were reversed, and AMD were looking to compensate for architectural deficiencies (and architectural design decisions that can either be claimed as erroneous or ahead of their time) via increased clockspeeds. However you look at these Bulldozer CPUs, the fact is that they remain some of the best overclockers of all time - at least when it comes to maximum operating frequencies, especially at absolutely scorching vCore values.

To achieve that operating frequency, Der8auer used an Elmor EVC2 controller and diagnostics chip, which, connected to a usually unpopulated pin area in the ASUS 970 PRO GAMING/AURA motherboard, allowed him to read-out everything that was running through the motherboard's VRM circuitry, and perform manual adjustments. Corsair Vengeance 2,666 MHz DDR3 memory was also used in the system. An accident happened along the way, though: when pulling AMD's stock cooler from the motherboard, the CPU remained attached to the cooler, which resulted in some bent pins (screams in horror). Luckily, things were fixed with a screwdriver - let that serve as a warning, alert, and tip, should this happen to you.

To achieve that operating frequency, Der8auer used an Elmor EVC2 controller and diagnostics chip, which, connected to a usually unpopulated pin area in the ASUS 970 PRO GAMING/AURA motherboard, allowed him to read-out everything that was running through the motherboard's VRM circuitry, and perform manual adjustments. Corsair Vengeance 2,666 MHz DDR3 memory was also used in the system. An accident happened along the way, though: when pulling AMD's stock cooler from the motherboard, the CPU remained attached to the cooler, which resulted in some bent pins (screams in horror). Luckily, things were fixed with a screwdriver - let that serve as a warning, alert, and tip, should this happen to you.