Fujitsu Introduces Its Own SandForce-powered Solid State Drives

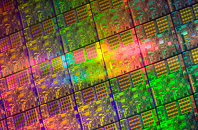

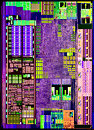

Former hard drive maker (it sold the HDD business to Toshiba in 2009) Fujitsu has finally decided to give SSDs (solid state drives) a try and so it developed and released such a storage solution. Codenamed HLACC2031A-G1, Fujitsu's SSD has a 2.5-inch form factor, a SATA 6.0 Gbps interface, a SandForce SF-2281 controller, MLC (multi-level cell) NAND Flash memory, and is capable of read/write speeds of up to 550/500 MB/s, and of a random read/write performance of 55,000/40,000 IOPS.

The HLACC2031A-G1 is first being shipped to APAC (Asia-Pacific) markets in two capacities - 120 GB (~ US$202) and 240 GB (~ US$427). Both models will come with a three-year warranty.

The HLACC2031A-G1 is first being shipped to APAC (Asia-Pacific) markets in two capacities - 120 GB (~ US$202) and 240 GB (~ US$427). Both models will come with a three-year warranty.