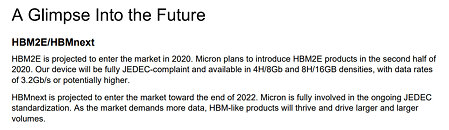

Micron Also Announces Development of HBMnext

Continuing from the Micron tech brief we shared earlier, a new interesting prospect for the future of ultra-bandwidth solutions is being called simply HBMnext. It's very likely this is only a working title for a next generation HBM memory interface, whether it is a mere evolution of HBM2E or HBM3 proper. The jump in memory speed from HBM2E to HBMnext is still under wraps; however, we've seen HBM2E take significant strides compared to HBM2 already. The first HBM2E products arrived with a 0.4 Gbps improvement over HBM2 (2.4 Gbps vs 2.0 Gbps), but HBM2E has already been certified - and is announced by Micron - as hitting 3.2 Gbps as soon as the second half of this year. One can expect HBMnext to take somewhat comparable strides. Users shouldn't expect to see HBMnext on any products soon, though; it's only expected to launch come 2022.