TSMC to Mark 3 nm Mass Production Start, Looking at Potential New Fabs in Japan and Germany

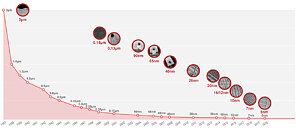

According to news out of Taiwan, TSMC will hold a ceremony to mark the official mass production start of its 3 nm node on the 29th of December. This is said to help "shatter doubts about de-Taiwanization" or in simpler terms, that Taiwan will lose its golden goose as TSMC invests abroad. The 3 nm fab—known as fab 18—is based in southern Taiwan's Tainan and the ceremony also marks the start of an expansion of TSMC's most advanced fab. TSMC is said to be kicking off its N3E node production sometime in the second half of 2023, followed by its N3P node in 2024, all of which should take place at fab 18, which also produces 5 nm wafers.

In related news, according to Reuters, a Japanese lawmaker from the ruling party has said that TSMC is considering a second plant in Japan, in addition to its current joint venture that is already under construction. TSMC's response to Reuters was that the company isn't ruling out Japan for future fabs, but that the company doesn't have any current plans. At the same time, TSMC is said to be sending executives to Dresden, Germany in early 2023, for a second round of talks about building a fab to help support the European auto industry, although this would be a 28/22 nm fab, which is far from cutting edge these days, although a lot more advanced than most fabs making chips for the auto industry.

In related news, according to Reuters, a Japanese lawmaker from the ruling party has said that TSMC is considering a second plant in Japan, in addition to its current joint venture that is already under construction. TSMC's response to Reuters was that the company isn't ruling out Japan for future fabs, but that the company doesn't have any current plans. At the same time, TSMC is said to be sending executives to Dresden, Germany in early 2023, for a second round of talks about building a fab to help support the European auto industry, although this would be a 28/22 nm fab, which is far from cutting edge these days, although a lot more advanced than most fabs making chips for the auto industry.