YMTC Develops 128 and 232-Layer Xtacking 4.0 NAND Memory Chips

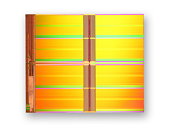

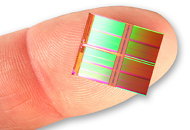

Chinese memory maker Yangtze Memory Technology Corp (YMTC) is allegedly preparing its next-generation Xtacking 4.0 3D NAND flash architecture for next-generation memory chips. According to the documentation obtained by Tom's Hardware, YMTC has developed two SKUs based on the upgraded Xtacking 4.0: X4-9060, a 128-layer three-bit-per-cell (TLC) 3D NAND, and the X4-9070, a 232-layer TLC 3D NAND. By using string stacking on both of these SKUs, YMTC plans to make the 3D NAND work by incorporating arrays with 64 and 116 active layers stacked on top of each other. This way, the export regulation rules from the US government are met, and the company can use the tools that are not under the sanction list.

While YMTC has yet to fully disclose the specific advantages of the Xtacking 4.0 technology, the industry anticipates significant enhancements in data transfer speeds and storage density. These improvements are expected to stem from increased plane counts for optimized parallel processing, refined bit/word line configurations to minimize latency, and the development of modified chip variants to boost production yields. When YMTC announced Xtacking 3.0, the company offered 128-layer TLC and 232-layer four-bit-per-cell (QLC) variants and was the first company to achieve 200+ layer count in the 3D NAND space. The Xtacking 3.0 architecture incorporates string stacking and hybrid bonding techniques and uses a mature process node for the chip's CMOS underlayer. We have to wait for the final Xtacking 4.0 details when YMTC's officially launches the SKUs.

While YMTC has yet to fully disclose the specific advantages of the Xtacking 4.0 technology, the industry anticipates significant enhancements in data transfer speeds and storage density. These improvements are expected to stem from increased plane counts for optimized parallel processing, refined bit/word line configurations to minimize latency, and the development of modified chip variants to boost production yields. When YMTC announced Xtacking 3.0, the company offered 128-layer TLC and 232-layer four-bit-per-cell (QLC) variants and was the first company to achieve 200+ layer count in the 3D NAND space. The Xtacking 3.0 architecture incorporates string stacking and hybrid bonding techniques and uses a mature process node for the chip's CMOS underlayer. We have to wait for the final Xtacking 4.0 details when YMTC's officially launches the SKUs.