U.S. Government Tightens Screws on Huawei's Global Chip Supply from TSMC

The U.S. government announced advanced measures that make it harder for foreign companies, such as Taiwan's TSMC, to supply chips to Chinese telecom hardware giant Huawei. Foreign companies that use American chipmaking equipment, are required to obtain a license from the U.S. before supplying certain chips to Huawei. Sources comment that the new rule was tailor-made to curb TSMC fabricating smartphone SoCs for Huawei's HiSilicon subsidiary.

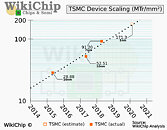

Mainland Chinese semiconductor companies are still behind Samsung and TSMC in 7 nm-class fab technologies, forcing HiSilicon to source from the latter. 7 nm fabrication is a key requirement for SoCs and modem chips capable of 5G. The high data transceiving rates of 5G requires a certain amount of compute power that can fit into smartphone-level power-envelopes only with the help of 7 nm, at least for premium smartphone form-factors. Same applies to 5G infrastructure equipment. This is hence perceived as a means for the U.S. to clamp brakes on Huawei's plans of playing a big role in 5G tech rollouts around the world, buying western 5G tech suppliers such as Nokia time to catch up. Huawei has been a flashpoint for a bitter political spat between the U.S. and China, with the Chinese press even threatening that the matter could hamper medical supplies to the U.S. to fight the COVID-19 pandemic.

Mainland Chinese semiconductor companies are still behind Samsung and TSMC in 7 nm-class fab technologies, forcing HiSilicon to source from the latter. 7 nm fabrication is a key requirement for SoCs and modem chips capable of 5G. The high data transceiving rates of 5G requires a certain amount of compute power that can fit into smartphone-level power-envelopes only with the help of 7 nm, at least for premium smartphone form-factors. Same applies to 5G infrastructure equipment. This is hence perceived as a means for the U.S. to clamp brakes on Huawei's plans of playing a big role in 5G tech rollouts around the world, buying western 5G tech suppliers such as Nokia time to catch up. Huawei has been a flashpoint for a bitter political spat between the U.S. and China, with the Chinese press even threatening that the matter could hamper medical supplies to the U.S. to fight the COVID-19 pandemic.