Monday, March 23rd 2020

TSMC N5P 5nm Node Offers 84-87% Transistor Density Gain Over Current 7nm Node

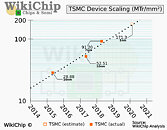

A WikiChip analysis of TSMC's next-generation 5 nanometer N5P silicon fabrication node estimates a massive 84-87% increase in transistor densities on offer compared to the company's first commercial 7 nm-class node, the N7 (7 nm DUV). The report estimates an 87% transistor-density increase, even though TSMC's own figure is slightly modest, at 84%. TSMC N5P node is expected to commence production later this year. Its precursor, TSMC N5, began risk production earlier this year, with production on the node commencing in April or May, unless derailed by the COVID-19 pandemic. The N5P node provides transistor densities of an estimated 171.3 million transistors per mm² die area, compared to 91.2 mTr/mm² of N7. Apple is expected to be the node's biggest customer in 2020, with the company building its A14-series SoC on it.

Source:

WikiChip

11 Comments on TSMC N5P 5nm Node Offers 84-87% Transistor Density Gain Over Current 7nm Node

N7 - "91.2 mTr/mm²" - 40-50 mTr real

N5P estimated 171.3 - 60-70 mTr real

So AMD shrinked their GPU by exactly 1,6, where it should have been 3.2x, so what can we expect from 84-85%. less than 42%.

While the "estimated" is for all types of memory and cache structures.

Going denser means harder to achieve the clock targets, and by default the designs go less dense in order to keep the clocks higher.

You can have a structure of few transistors ticking at insane clocks.

All these production processes have a high density and high performance variations. Manufacturer quoted numbers are obviously high density ones. High performance variation is about 30% less dense. Almost all computer CPUs and GPUs are made on the high performance variation (for obvious reasons), high density tends to be mostly mobile chips.

Edit:

Also, @ARF has a good point that logic is less dense than manufacturer quoted numbers that are usually a variation of memory (SRAM seems to be common). This causes additional reduction in density.

From what both AMD and Intel have said about this, IO seems to be another pain point for scaling as it does not scale as well (probably for obvious reasons).N5P is expected to commence risk production in Q2 2020.

16NM performance is 28, average transistor in RX 580 - 25 mTr, only 3 mTr difference.

30% less dense means 65, so the ZEN2 comes really close with 50 mTr because of the L3 cache cells that must be the only 77 mTr element in there.

www.techcenturion.com/7nm-10nm-14nm-fabrication