Cadence and Intel Collaborate to Enable a 14 nm Tri-gate Design Platform

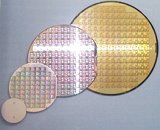

Cadence Design Systems, Inc., a leader in global electronic design automation, and Intel Corporation, a world leader in computing innovation, today announced that the companies are collaborating to support Intel's 14 nm Tri-Gate process technology to enable customers of Intel Custom Foundry.

Cadence and Intel have together enabled the custom/analog flow, including Spectre APS, Virtuoso Schematic Editor, Virtuoso Layout Suite and Virtuoso Analog Design Environment for the 14nm Tri-Gate process. The companies are also collaborating on the development of the Cadence digital flow featuring Encounter Digital Implementation System, QRC Extraction Solution, and Tempus Timing Signoff Solution. Using these design flows, customers can leverage the power, performance and area benefits of Intel's 14 nm process technology.

Cadence and Intel have together enabled the custom/analog flow, including Spectre APS, Virtuoso Schematic Editor, Virtuoso Layout Suite and Virtuoso Analog Design Environment for the 14nm Tri-Gate process. The companies are also collaborating on the development of the Cadence digital flow featuring Encounter Digital Implementation System, QRC Extraction Solution, and Tempus Timing Signoff Solution. Using these design flows, customers can leverage the power, performance and area benefits of Intel's 14 nm process technology.