Monday, February 24th 2020

PCI-Express Gen 6 Reaches Development Milestone, On Track for 2021 Rollout

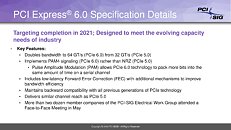

The PCI-Express gen 6.0 specification reached an important development milestone, with the publication of its version 0.5 first-draft. This provides important pointers to PCI-SIG members on what features and design changes gen 6.0 hopes to bring, and what its all important number is - bandwidth. PCIe gen 6.0 quadruples per-lane bandwidth over gen 4.0 to 64 GT/s (double that of gen 5.0), resulting in bi-directional bandwidth of 256 GB/s in an x16 configuration.

The spec also introduces a new physical layer change, with PAM4 (pulse amplitude modulation) signaling replacing NRZ (non-return to zero), a key ingredient in the generational bandwidth doubling effort. Despite this, PCIe gen 6.0 retains backwards-compatibility with all older generations of PCIe, which could mean the PCIe slot on motherboards may not look any different. PCIe gen 6.0 also introduces FEC (forward error-correction), and has similar per-channel reach as PCIe gen 5.0. Our older article on Intel's proprietary CXL outlines a key feature of PCIe gen 5.0 besides its bandwidth doubling over gen 4.0 - scalability. Although targeting completion in 2021, it could take several more years for the technology to transcend enterprise computing segments and reach the client. PCI-SIG anticipates the need for gen 6.0 kind of bandwidth in the industry by 2025.

Source:

AnandTech

The spec also introduces a new physical layer change, with PAM4 (pulse amplitude modulation) signaling replacing NRZ (non-return to zero), a key ingredient in the generational bandwidth doubling effort. Despite this, PCIe gen 6.0 retains backwards-compatibility with all older generations of PCIe, which could mean the PCIe slot on motherboards may not look any different. PCIe gen 6.0 also introduces FEC (forward error-correction), and has similar per-channel reach as PCIe gen 5.0. Our older article on Intel's proprietary CXL outlines a key feature of PCIe gen 5.0 besides its bandwidth doubling over gen 4.0 - scalability. Although targeting completion in 2021, it could take several more years for the technology to transcend enterprise computing segments and reach the client. PCI-SIG anticipates the need for gen 6.0 kind of bandwidth in the industry by 2025.

33 Comments on PCI-Express Gen 6 Reaches Development Milestone, On Track for 2021 Rollout

Sure, but it's still crappy.

- X-series Motherboards see the total x20 or x24 6.0 lanes converted to a total of x40/x48 5.0 lanes or even x80/x96 4.0 lanes or some combination thereof of 4.0 and 5.0 lanes.

- B-series Motherboards see the 6.0 lanes converted to x80/x96 4.0 lanes

- A-series Motherboards see the 6.0 lanes converted to 1 x16 PCIe 4.0 GPU Slot and 1 x4 NVMe Slot, and the remaining 6.0 lanes converted to x120/x152 3.0 lanes.

With PCIe 4.0 and 5.0 needing redrivers/signal repeaters, it'll take a long while of usage in the consumer space before those ever become cheap enough, or if there's a material breakthrough in room temperature superconductors that does away with them (or a complete design shift to the next motherboard and PSU standard). So aside from halo X-series Motherboards pushing 5.0, cheaper ones might only use 5.0 for the 1st GPU and 1st NVMe drive, and the rest using 4.0, which is good enough for future-proofing for awhile, considering that only storage and Ethernet have immediate benefits from more bandwidth (assuming one has the appropriate add-in cards).PCIe 6.0 will really only be useful for cloud datacenters and research institutions that need more than 500 GbE networking, as beyond that there isn't yet any sort of non-proprietary hardware that could really utilize that amount of bandwidth, especially not at the consumer level. Further, it might be preferable to use cables for PCIe 5.0 and 6.0, considering that they're cheaper than relying on retimers/redrivers and specialized PCBs. Kind of like the PCIe version of the classic SATA cable, but now plugging into add-in cards alongside the power cables (or maybe even replacing the power cables; should the shift to pure 12v PSUs and motherboards mean redesigning power delivery as a whole).

Hey everyone's for progress, at least the vast majority of people in this field are but the major issue we as consumers face is the exorbitant premiums we have to shell often times for unfinished & jerky/quirky implementations which ideally should've ironed out in the testing phase. Till the time companies rush out things, like that Galaxy

Foldflop, in th name of unique we'll continue seeing aversion towards better adoption of such technologies.It'll likely come with DDR5 support. PCIe 6.0 is still 2 years too early even for Intel. It'll be 2022 before we see anything sporting the latest standard & even that is a stretch given we still don't have PCIe 5.0 hardware.It looks like it has everything to do with power from what I can tell...