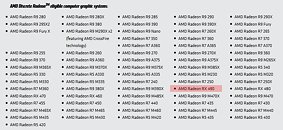

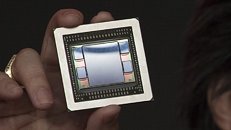

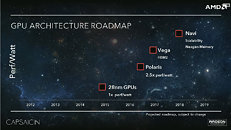

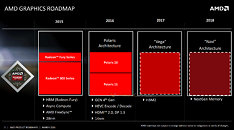

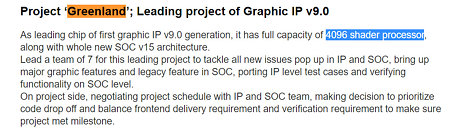

AMD's upcoming GPUs based on the "Polaris" and "Vega" architectures appear to be taking advantage of performance/Watt gains to keep stream processor counts low, and chips small, according to a VideoCardz analysis of curious-looking CompuBench entries. Assuming that a Graphics CoreNext (GCN) compute unit (CU) of the "Polaris" architecture, like the three versions of GCN before it, consists of 64 stream processors, AMD's Polaris 11 silicon, codenamed "Baffin," could feature over 1,024 stream processors, across 16 CUs; Polaris 10, codenamed "Ellesmere," could feature over 2,304 stream processors spread across over 36 CUs; and Vega 10 featuring 4,096 stream processors, spread across 64 CUs.

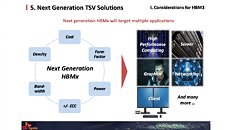

The "Baffin" silicon succeeds current generation "Curacao" silicon, driving mid-range graphics cards. It is expected to feature a 128-bit wide GDDR5 memory interface, holding 4 GB of memory. The "Ellesmere" silicon succeeds current-generation "Tonga" silicon, driving performance-segment SKUs. It could feature up to 8 GB of GDDR5(X) memory. These two chips could see the light of the day by mid-2016. The third chip out of AMD's stable, Vega 10, could succeed "Fiji," overcoming its biggest marketing shortcoming - 4 GB memory. Taking advantage of HBM2 interface, it could feature 16 GB of memory. It could launch some time in early-2017. AMD is

claiming a massive 2.5X performance-per-Watt increase for "Polaris" over the current GCN 1.2 architecture, which drives the "Tonga" and "Fiji" chips, and so these stream processor counts could look deceptively insufficient.