Samsung Foundry Renames 3 nm Process to 2 nm Amid Competition with Intel

In a move that could intensify competition with Intel in the cutting-edge chip manufacturing space, Samsung Foundry has reportedly decided to rebrand its second-generation 3 nm-class fabrication technology, previously known as SF3, to a 2 nm-class manufacturing process called SF2. According to reports from ZDNet, the renaming of Samsung's SF3 to SF2 is likely an attempt by the South Korean tech giant to simplify its process nomenclature and better compete against Intel Foundry, at least visually. Intel is set to roll out its Intel 20A production node, a 2 nm-class technology, later this year. The reports suggest that Samsung has already notified its customers about the changes in its roadmap and the renaming of SF3 to SF2. Significantly, the company has reportedly gone as far as re-signing contracts with customers initially intended to use the SF3 production node.

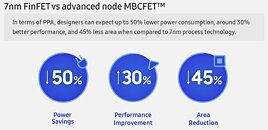

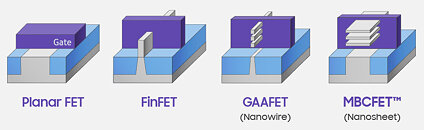

"We were informed by Samsung Electronics that the 2nd generation 3 nm [name] is being changed to 2 nm," an unnamed source noted to ZDNet. "We had contracted Samsung Foundry for the 2nd generation 3 nm production last year, but we recently revised the contract to change the name to 2 nm." Despite the name change, Samsung's SF3, now called SF2, has not undergone any actual process technology alterations. This suggests that the renaming is primarily a marketing move, as using a different process technology would require customers to rework their chip designs entirely. Samsung intends to start manufacturing chips based on the newly named SF2 process in the second half of 2024. The SF2 technology, which employs gate-all-around (GAA) transistors that Samsung brands as Multi-Bridge-Channel Field Effect Transistors (MBCFET), does not feature a backside power delivery network (BSPDN), a significant advantage of Intel's 20A process. Samsung Foundry has not officially confirmed the renaming.

"We were informed by Samsung Electronics that the 2nd generation 3 nm [name] is being changed to 2 nm," an unnamed source noted to ZDNet. "We had contracted Samsung Foundry for the 2nd generation 3 nm production last year, but we recently revised the contract to change the name to 2 nm." Despite the name change, Samsung's SF3, now called SF2, has not undergone any actual process technology alterations. This suggests that the renaming is primarily a marketing move, as using a different process technology would require customers to rework their chip designs entirely. Samsung intends to start manufacturing chips based on the newly named SF2 process in the second half of 2024. The SF2 technology, which employs gate-all-around (GAA) transistors that Samsung brands as Multi-Bridge-Channel Field Effect Transistors (MBCFET), does not feature a backside power delivery network (BSPDN), a significant advantage of Intel's 20A process. Samsung Foundry has not officially confirmed the renaming.