Monday, November 16th 2020

TSMC Achieves Major Breakthrough in 2 nm Manufacturing Process, Risk Production in 2023

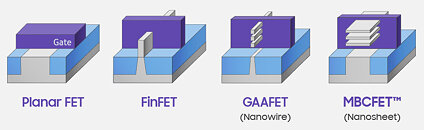

The Taiwan Economic Daily claims that TSMC has achieved a major internal breakthrough for the eventual rollout of 2 nm fabrication process technology. According to the publication, this breakthrough has turned TSMC even more optimistic towards a 2023 rollout of 2 nm risk production - which is all the more impressive considering reports that TSMC will be leaving the FinFet realm for a new multi-bridge channel field effect transistor (MBCFET) architecture - itself based on the Gate-All-Around (GAA) technology. This breakthrough comes one year after TSMC put together an internal team whose aim was to pave the way for 2 nm deployment.

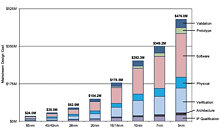

MBCFET expands on the GAAFET architecture by taking the Nanowire field-effect transistor and expanding it so that it becomes a Nanosheet. The main idea is to make the field-effect transistor three-dimensional. This new complementary metal oxide semiconductor transistor can improve circuit control and reduce leakage current. This design philosophy is not exclusive to TSMC - Samsung has plans to deploy a variant of this design on their 3 nm process technology. And as has been the norm, further reductions in chip fabrication scale come at hefty costs - while the development cost for 5 nm has already achieved $476M in cost, Samsung reports that their 3 nm GAA technology will cost in excess of $500M - and 2 nm, naturally, will come in even costlier than that.

Source:

Gizchina

MBCFET expands on the GAAFET architecture by taking the Nanowire field-effect transistor and expanding it so that it becomes a Nanosheet. The main idea is to make the field-effect transistor three-dimensional. This new complementary metal oxide semiconductor transistor can improve circuit control and reduce leakage current. This design philosophy is not exclusive to TSMC - Samsung has plans to deploy a variant of this design on their 3 nm process technology. And as has been the norm, further reductions in chip fabrication scale come at hefty costs - while the development cost for 5 nm has already achieved $476M in cost, Samsung reports that their 3 nm GAA technology will cost in excess of $500M - and 2 nm, naturally, will come in even costlier than that.

39 Comments on TSMC Achieves Major Breakthrough in 2 nm Manufacturing Process, Risk Production in 2023

Competition hotting up in the race to 2nm and 3nm whilst your 10nm process is still so broken that you can't scale it up to desktops and servers, and your PHB's put all the eggs in the 7nm basket which has already been pushed back by more time that its total development cycle was supposed to last.

So any optical guys out there know when one would have to transition from EUV light to x-rays lithography?

All similarly bad practices confuse... well, suppose everyone - something may be 2nm, but we are lead to believe that it's... 7 times better than 14nm - which I seriously doubt...

What they need to talk about and show us is density (millions of transistors per square millimeter), power consumption and frequency.

If Intel had been less ambitious with 10nm and just worked on a simpler jump, (ie, still 10nm but not trying multiple high-risk industry-firsts like Cobalt, COAG, and 36nm pitch without EUV) they likely wouldn't be in the mess they're in right now.

credit: extremetech+wikichip

Density will continue to scale well and the power consumption will decrease a bit, however with Dennard scaling hitting a wall, don't expect any significant increases in clock frequencies. CPU architectures will have to go wider and deeper to increase single core performance. GPUs can have significant performance increases by having more execution units at almost the same or even lower clocks.Not an optical guy, but as a device architect, I don't think it'll happen for silicon. Multipatterning EUV is enough to hit the limitations of silicon. We'll see short channel effects making silicon unsuitable for any further scaling before the need for x-ray lithography arises. 3D stacking can extend the life of silicon for a little bit longer, before moving to alternate materials.