Intel to Disable Rudimentary AVX-512 Support on Alder Lake Processors

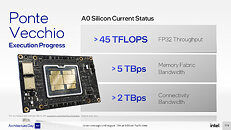

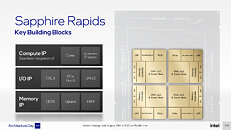

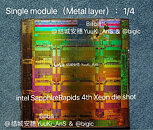

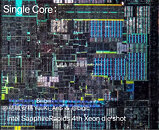

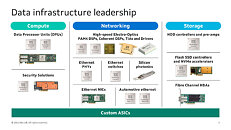

Intel is reportedly disabling the rudimentary AVX-512 instruction-set support on its 12th Gen Core "Alder Lake" processors using a firmware/ME update, reports Igor's Lab. Intel does not advertise AVX-512 for Alder Lake, even though the instruction-set was much publicized for a couple of its past-generation client-segment chips, namely 11th Gen Rocket Lake, and 10th Gen Cascade Lake-X HEDT processors. The company will likely make AVX-512 a feature that sets apart its next-gen HEDT processors derived from Sapphire Rapids, its upcoming enterprise microarchitecture.

AVX-512 is technically not advertised for Alder Lake, but software that calls for these instructions can utilize them on certain 12th Gen Core processors, when paired with older versions of the Intel ME firmware. The ME version Intel releases to OEMs and motherboard vendors alongside its upcoming 65 W Core desktop processors, and the Alder Lake-P mobile processors, will prevent AVX-512 from being exposed to the software. Intel's reason to deprecate what little client-relevant AVX-512 instructions it had for Core processors, could have do with energy efficiency, as much as lukewarm reception from client software developers. The instruction is more relevant to the HPC and cloud-computing markets.Many Thanks to TheoneandonlyMrK for the tip.

AVX-512 is technically not advertised for Alder Lake, but software that calls for these instructions can utilize them on certain 12th Gen Core processors, when paired with older versions of the Intel ME firmware. The ME version Intel releases to OEMs and motherboard vendors alongside its upcoming 65 W Core desktop processors, and the Alder Lake-P mobile processors, will prevent AVX-512 from being exposed to the software. Intel's reason to deprecate what little client-relevant AVX-512 instructions it had for Core processors, could have do with energy efficiency, as much as lukewarm reception from client software developers. The instruction is more relevant to the HPC and cloud-computing markets.Many Thanks to TheoneandonlyMrK for the tip.