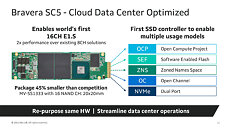

Marvell Announces Bravera, World's First PCIe 5.0 SSD Controllers

Marvell today announced its new Bravera SC5 controller family, bringing unprecedented performance, best-in-class efficiency, and leading security features to address ever-expanding workloads in the cloud. The massive amount of data to be processed in cloud data centers is driving demand for faster and higher bandwidth storage in these environments. Marvell's Bravera SC5 SSD controllers address the critical requirements for scalable, containerized cloud storage infrastructure. By enabling the highest performing flash storage solutions, Marvell's controllers are poised to be the foundation for data centers that offer ultra-low latency, real-time applications while also providing cost-optimized, cloud-scale capacity.

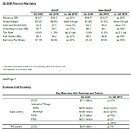

As the industry's first SSD controllers to support PCIe 5.0 and NVMe 1.4b, Marvell's Bravera SC5 doubles the performance compared to PCIe 4.0 SSDs. This contributes to accelerated workloads and reduced latency, dramatically improving the user experience. In order to meet cloud service providers' stringent security requirements to ensure users' data is safe and protected, the controllers offer FIPS-compliant root of trust (RoT), AES 256-bit encryption and multi-key revocation. The new controllers are the first with a hardware-based Elastic SLA Enforcer to assure quality of service (QoS) and provide metering capabilities per customer to increase overall storage efficiency and utilization while lowering total cost of ownership (TCO).

As the industry's first SSD controllers to support PCIe 5.0 and NVMe 1.4b, Marvell's Bravera SC5 doubles the performance compared to PCIe 4.0 SSDs. This contributes to accelerated workloads and reduced latency, dramatically improving the user experience. In order to meet cloud service providers' stringent security requirements to ensure users' data is safe and protected, the controllers offer FIPS-compliant root of trust (RoT), AES 256-bit encryption and multi-key revocation. The new controllers are the first with a hardware-based Elastic SLA Enforcer to assure quality of service (QoS) and provide metering capabilities per customer to increase overall storage efficiency and utilization while lowering total cost of ownership (TCO).