Monday, May 3rd 2021

Intel "Sapphire Rapids" Xeon Processor Could Feature Up To 80 Cores: New Leak

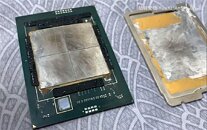

Intel's upcoming Xeon "Sapphire Rapids" enterprise processor come come with CPU core-counts as high as 80, according to the latest round of photo-leaks. An earlier article predicted the chip cram up to 56 cores alongside on-package HBM. The processor reportedly features up to 80 cores, spread across four 20-core chiplets. Unlike on the latest AMD EPYC processor, there doesn't appear to be a centralized I/O controller die. This particular processor is based in the LGA4189 package, which features additional pins compared to the LGA4577-X socket from the 56-core leak. The newer socket has additional pins that enable next-gen I/O, which include PCI-Express Gen 5.0, and CXL 1.1 interface.

Source:

HotHardware

36 Comments on Intel "Sapphire Rapids" Xeon Processor Could Feature Up To 80 Cores: New Leak

There are only 4 of them as shown in the image.

At high frequencies the physical distance matter for propagation delay and signal integrity. That is the time and distance the electrons have to travel matters.

So Intel might be trying to keep latency low as their architecture tends to be.

CPUs that are build for use in quad socket systems.

I think you got these packages backwards as the 4189 - 5 was rumoured to be up to 56 Cores for Ice Lake, and i'm not sure how LGA 4189 can have more pins than LGA 4577.

yet on re-reading, its all worded correctly our brains are just bad

gluechiplet now they using it? Wonder if they're still clinging to core to core latency advantages :rolleyes:This is a natural 1.0 chiplet solution. AMD's Zen 2 introduced the I/O die, which has performed far better than I expected. NVidia's multi-GPU solution (NVLink / NVSwitch) also uses an I/O die of sorts, so the switched "central" I/O design is probably the superior design.

Still, given how UPI / Hypertransport was already designed for inter-chip communication (aka: without an I/O die and just wiring up the chips together), it makes sense to start with this design first. In both cases, latency will go up compared to a single die solution, but I think Zen2 / NVidia NVSwitch has proven that latency can go up by dramatic amounts and yet we can still write software that works with that kind of latency.

---------

Laptops / Desktops are traditionally single-core programmed. But if more and more code (aka: video games or other software) keep getting better and better at latency hiding / multicore compute, maybe the processor of the future will have even higher latency. Or maybe, Apple M1 / Cell phones will snap us back into traditional, lower-latency architectures.

Xeon 9180P (guess on name) - 80C/160T?, MSRP $15000

Remember when people laughed at AMD for moar cores?

The stock cooler will have it thermal shutdown when at max load

And a 360mm AIO will keep it at 100C