Sunday, April 19th 2020

TSMC 3nm Process Packs 250 Million Transistors Per Square Millimeter

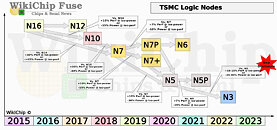

Imagine being able to shrink a Pentium 4 processor die to the size of a pin-head (if you can figure out how to place 478 bumps on it). TSMC revealed that its future 3 nanometer silicon fabrication node has a development target of 250 million transistors per mm². Called N3, the next-generation silicon fabrication node succeeds TSMC's N5 family of 5 nm-class nodes (that's N5 and any possible refinements).

TSMC CEO CC Wei confirmed that development of the 3 nm node is on-track, with risk production scheduled for 2021 and volume production commencing in the second half of 2022. Perhaps the most startling revelation is that TSMC has decided to stick with FinFETs for N3 owing to the maturity of the technology. Experts are of the opinion that sub-5 nm nodes will require major innovations with materials and structures. TSMC claims that N3 will provide a 10-15% speed improvement at iso-power or 25-30% power reduction at iso-speed, compared to N5.

Source:

WikiChip Fuse

TSMC CEO CC Wei confirmed that development of the 3 nm node is on-track, with risk production scheduled for 2021 and volume production commencing in the second half of 2022. Perhaps the most startling revelation is that TSMC has decided to stick with FinFETs for N3 owing to the maturity of the technology. Experts are of the opinion that sub-5 nm nodes will require major innovations with materials and structures. TSMC claims that N3 will provide a 10-15% speed improvement at iso-power or 25-30% power reduction at iso-speed, compared to N5.

32 Comments on TSMC 3nm Process Packs 250 Million Transistors Per Square Millimeter