Sunday, February 28th 2021

AMD "Genoa" Expected to Cram Up to 96 Cores, MCM Imagined

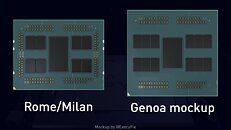

AMD's next-generation EPYC enterprise processor that succeeds the upcoming 3rd Gen EYPIC "Milan," codenamed "Genoa," is expected to be the first major platform update for AMD's enterprise platforms since the 2017 debut of the "Zen" based "Naples." Implementing the latest I/O interfaces, such as DDR5 memory and PCI-Express gen 5.0, the chip will also increase CPU core counts by 50% over "Milan," according to ExecutableFix on Twitter, a reliable source with rumors from the semiconductor industry. To enable the goals of new I/O and increased core counts, AMD will transition to a new CPU socket type, the SP5. This is a 6,096-pin land grid array (LGA), and the "Genoa" MCM package on SP5 is imagined to be visibly larger than SP3-generation packages.

With the added fiberglass substrate real-estate, AMD is expected to add more CPU chiplets to the package, and ExecutableFix expects the chiplet count to be increased to 12. AMD is expected to debut the "Zen 4" microarchitecture in the enterprise space with "Genoa," with the CPU chiplets expected to be built on the 5 nm EUV silicon fabrication node. Assuming the chiplets still only pack 8 cores a piece, "Genoa" could cram up to 96 cores per socket, or up to 192 logical processors, with SMT enabled.The sIOD die (I/O complex) is another component with major changes. AMD is expected to increase the memory bus width by 50%, with the processor now expected to come with as 12-channel DDR5 memory interface, natively supporting DDR5-5333. The PCI-Express lane budget appears unchanged, with up to 128 lanes per socket, but implements the latest PCI-Express gen 5.0, which is expected to double bandwidth over the current PCIe gen 4.0. In a bid to reduce the die-size of the sIOD, and more importantly its TDP, AMD might finally build it on newer silicon fabrication nodes, such as 7 nm. ExecutableFix expects the overall TDP of "Genoa" to be around 320 W, configurable up to 400 W.

AMD is expected to debut "Genoa" only by mid/late 2022, as it is yet to monetize the 3rd Gen EPYC "Milan."

Sources:

ExecutableFix (Twitter) 1, ExecutableFix (Twitter) 2, via Videocardz

With the added fiberglass substrate real-estate, AMD is expected to add more CPU chiplets to the package, and ExecutableFix expects the chiplet count to be increased to 12. AMD is expected to debut the "Zen 4" microarchitecture in the enterprise space with "Genoa," with the CPU chiplets expected to be built on the 5 nm EUV silicon fabrication node. Assuming the chiplets still only pack 8 cores a piece, "Genoa" could cram up to 96 cores per socket, or up to 192 logical processors, with SMT enabled.The sIOD die (I/O complex) is another component with major changes. AMD is expected to increase the memory bus width by 50%, with the processor now expected to come with as 12-channel DDR5 memory interface, natively supporting DDR5-5333. The PCI-Express lane budget appears unchanged, with up to 128 lanes per socket, but implements the latest PCI-Express gen 5.0, which is expected to double bandwidth over the current PCIe gen 4.0. In a bid to reduce the die-size of the sIOD, and more importantly its TDP, AMD might finally build it on newer silicon fabrication nodes, such as 7 nm. ExecutableFix expects the overall TDP of "Genoa" to be around 320 W, configurable up to 400 W.

AMD is expected to debut "Genoa" only by mid/late 2022, as it is yet to monetize the 3rd Gen EPYC "Milan."

26 Comments on AMD "Genoa" Expected to Cram Up to 96 Cores, MCM Imagined

The whole idea of chiplets is to not put too many apples in one basket. Desktop wise, from a latency perspective it would be nice to have 12-16c ccd's sure...

But DDR5 (higher frequency lower latency IF) will help that as well.