Sunday, February 28th 2021

AMD "Genoa" Expected to Cram Up to 96 Cores, MCM Imagined

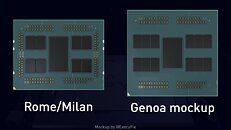

AMD's next-generation EPYC enterprise processor that succeeds the upcoming 3rd Gen EYPIC "Milan," codenamed "Genoa," is expected to be the first major platform update for AMD's enterprise platforms since the 2017 debut of the "Zen" based "Naples." Implementing the latest I/O interfaces, such as DDR5 memory and PCI-Express gen 5.0, the chip will also increase CPU core counts by 50% over "Milan," according to ExecutableFix on Twitter, a reliable source with rumors from the semiconductor industry. To enable the goals of new I/O and increased core counts, AMD will transition to a new CPU socket type, the SP5. This is a 6,096-pin land grid array (LGA), and the "Genoa" MCM package on SP5 is imagined to be visibly larger than SP3-generation packages.

With the added fiberglass substrate real-estate, AMD is expected to add more CPU chiplets to the package, and ExecutableFix expects the chiplet count to be increased to 12. AMD is expected to debut the "Zen 4" microarchitecture in the enterprise space with "Genoa," with the CPU chiplets expected to be built on the 5 nm EUV silicon fabrication node. Assuming the chiplets still only pack 8 cores a piece, "Genoa" could cram up to 96 cores per socket, or up to 192 logical processors, with SMT enabled.The sIOD die (I/O complex) is another component with major changes. AMD is expected to increase the memory bus width by 50%, with the processor now expected to come with as 12-channel DDR5 memory interface, natively supporting DDR5-5333. The PCI-Express lane budget appears unchanged, with up to 128 lanes per socket, but implements the latest PCI-Express gen 5.0, which is expected to double bandwidth over the current PCIe gen 4.0. In a bid to reduce the die-size of the sIOD, and more importantly its TDP, AMD might finally build it on newer silicon fabrication nodes, such as 7 nm. ExecutableFix expects the overall TDP of "Genoa" to be around 320 W, configurable up to 400 W.

AMD is expected to debut "Genoa" only by mid/late 2022, as it is yet to monetize the 3rd Gen EPYC "Milan."

Sources:

ExecutableFix (Twitter) 1, ExecutableFix (Twitter) 2, via Videocardz

With the added fiberglass substrate real-estate, AMD is expected to add more CPU chiplets to the package, and ExecutableFix expects the chiplet count to be increased to 12. AMD is expected to debut the "Zen 4" microarchitecture in the enterprise space with "Genoa," with the CPU chiplets expected to be built on the 5 nm EUV silicon fabrication node. Assuming the chiplets still only pack 8 cores a piece, "Genoa" could cram up to 96 cores per socket, or up to 192 logical processors, with SMT enabled.The sIOD die (I/O complex) is another component with major changes. AMD is expected to increase the memory bus width by 50%, with the processor now expected to come with as 12-channel DDR5 memory interface, natively supporting DDR5-5333. The PCI-Express lane budget appears unchanged, with up to 128 lanes per socket, but implements the latest PCI-Express gen 5.0, which is expected to double bandwidth over the current PCIe gen 4.0. In a bid to reduce the die-size of the sIOD, and more importantly its TDP, AMD might finally build it on newer silicon fabrication nodes, such as 7 nm. ExecutableFix expects the overall TDP of "Genoa" to be around 320 W, configurable up to 400 W.

AMD is expected to debut "Genoa" only by mid/late 2022, as it is yet to monetize the 3rd Gen EPYC "Milan."

26 Comments on AMD "Genoa" Expected to Cram Up to 96 Cores, MCM Imagined

Core count is just one reason to upgrade, consolidation of many boxes to few for power savings is another, and more of everything else... I/O memory... w/e.

I am just happy to see AMD adopting OAM for compute and OCP for nics, its nice to see open standards being used.

Frontier or El Capitan MI200 OAM + Genoa

What, 5 years ago we had 8 core CPU's in the server space and now thanks to AMD that numbers skyrocketing - and we all benefit in the background from faster, more power efficient servers

5 years ago Intel had Broadwell-based Xeons? 4-24 cores.

Bulldozer/Piledriver Opterons had 4-16 cores.

Cramming 12 cores on chiplet would make sense on 5 nm if the yield is good enough - and thanks to Apple's 1-year headstart, it will probably be good enough. It would reduce the amount of (slow) chiplet-to-chiplet communication and the complexity of the (already giant) I/O die.

24 in 2016, 32 in 2017, 64 in 2019, 96 in 2022.

Before that it was 18 in 2014, 15 in 2014 and 8 back in 2012.

AMD had Opterons since 2011-2012 that were 16 thread, 8 module CMT.

But larger picture - you have had that possibility for a while but not necessarily for end-users in customer space. Multi-socket servers are an implementation of exactly the same idea.

You can have 2x 64-core EPYCs in one system today. And if you happen to operate a nuclear power plant, 8x 28-core Xeons :D

Either way, it's a little more complicated than just getting more cores. There have been process improves, architectural improvements, improvement in design software to build these chips, etc. I'm just glad that it's normal to see 8c chips in laptops these days.

I wonder what this will mean for AM5 chips?

The plausibility of it though it quite cool to think about. I've actually said similar before on these forums, but I hadn't quite envisioned it the way I just described to the same extent and the more I think about it to me that seems one of the most optimal ways to do it. I think mounting the GPU's more close to the CPU/Memory would also be beneficial. Which with GPU's going MCM could be done the same way on the opposite side of the memory banks. You might channel interleave them even GPU/CPU/GPU/CPU along with the memory itself. If AMD were to do that I'd suggest a black, red, and grey substrate perhaps to differentiate between CPU/GPU/FPGA chips.

What I've mentioned before is more of a return to the older arcade board chip rom socketed setup which really this would be a condensed form of actually, but it would be clean with short memory traces and highly adaptable based on what sockets you integrate for what reasons.