Friday, June 11th 2021

AMD Shares New Details on Their 3D V-Cache Tech for Zen 3+

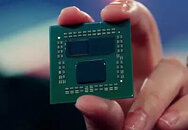

AMD via its official YouTube has shared a video that goes into slightly more detail on their usage of V-Cache on the upcoming Zen 3+ CPUs. Firstly demoed to the public on AMD's Computex 2021 event, the 3D V-Cache leverages TSMC's SoIC stacking technology, which enables silicon developments along the Z axis, instead of the more usual footprint increase along the X axis. The added 3D V-Cache, which was shown in Computex as being deployed in a prototype Ryzen 9 5900X 12-core CPU, adds 64 MB of L3 cache to each CCX (the up-to-eight-cores core complex on AMD's latest Zen design), basically tripling the amount of L3 cache available for the CPU. This, in turn, was shown to increase FPS in games quite substantially (somewhere around 15%), as games in particular are sensitive to this type of CPU resources.

The added information explains that there is no usage of microbumps - instead, there is a perfect alignment between the bottom layer (with the CCX) and the top layer (the L3 cache) which enables the bonding process to occur naturally via the TSVs (Through Silicon Vias) already present in the silicon, in a zero-gap manner, between both halves of the CPU-cache sandwich. To enable this, AMD flipped the CCX upside down (the core complex now faces the bottom of the chip, instead of the top), shaved 95% of the silicon on top of the upside-down core complexes, and then attaches the 3D V-Cache chips on top of this formation. This also has the added bonus of decreasing the distance between the L3 cache and the CCX (the distance between both in the Z axis is around 1,000 times smaller than if the L3 cache was deployed in the classical X axis), which decreases power consumption, temperatures, and latency, allowing for further increases to system performance. Look after the break for the full video.

Source:

AMD

The added information explains that there is no usage of microbumps - instead, there is a perfect alignment between the bottom layer (with the CCX) and the top layer (the L3 cache) which enables the bonding process to occur naturally via the TSVs (Through Silicon Vias) already present in the silicon, in a zero-gap manner, between both halves of the CPU-cache sandwich. To enable this, AMD flipped the CCX upside down (the core complex now faces the bottom of the chip, instead of the top), shaved 95% of the silicon on top of the upside-down core complexes, and then attaches the 3D V-Cache chips on top of this formation. This also has the added bonus of decreasing the distance between the L3 cache and the CCX (the distance between both in the Z axis is around 1,000 times smaller than if the L3 cache was deployed in the classical X axis), which decreases power consumption, temperatures, and latency, allowing for further increases to system performance. Look after the break for the full video.

37 Comments on AMD Shares New Details on Their 3D V-Cache Tech for Zen 3+

Additionally, it's important to understand that gaming performance isn't a benchmark of CPU performance, despite the fact the CPU performance being important. The CPU only needs to be fast enough to not bottle neck the GPU, which is why we typically see diminishing returns with higher CPU speeds in gaming, first the FPS gains dry out, beyond that we gain better frame time consistency, until there are no more gains.

With current games, Skylake and Zen 3 already hit this point in most games around ~4.3-4.5 GHz. So even if this new CPU is significantly faster, it might not materialize as increased gaming performance, unless you underclock the CPUs as you mentioned.Guys, you should refrain from using big words like IPC when you clearly don't understand what it means ;)

IPC means instructions per clock, and is a measure of the average instructions per clock the architecture is capable of. IPC is not performance, but an underlying constant of the architecture which is independent of how many threads or cores which are involved, and is also workload independent. We usually use a single thread and a wide selection of workloads to approximate the relative IPC between different CPUs.

But whenever people mention "multithreaded IPC", "application specific IPC", SMT in relation to IPC, etc. that's a dead giveaway that they are clueless about what IPC really is. They are in fact talking about performance, not IPC.Do we have any actual evidence of the existence of "Zen 3+"?

Could it be that it was invented by the "leakers"?

If IPC is some constant as you state, please give the IPC figure of any processsor currently in production, as a floating point number, and how that was measured.

edit: also, who the f is ”we” in your text?

you seem to be describing what relative single threaded performance at a fixed clock frequency is. That has very little to do with ”IPC”.

Leaving final speeds and performance relatively wide open on purpose, imagine Intel's engineering spec team now, I bet they're in work this weekend.

There's a cache per CCD AFAIK ?!

As for thermal worries, we've had them year's, they're not going away. ..

I would love to get my hands on that and see the impact of this cache. I'm interested in the impact on heat, voltage/current and clocks.

There's rumour about Zen3+ being a slightly new design compared to Zen3 with extra IPC improvements, but those rumours are conflicting as hell, some says they cancelled it, some says it hasn't been there to cancel it in the first place, and some says it's just the exact same Zen3 design with the V-Cache, that's why there are many conflicting rumours around which makes all these rumours plausible in the same time.

If they found out zen3 works well for minimal cost but good gains just by adding the V-cache, they'd shuffle the new designs and ideas off for AM5 chips instead

I really think AMD should release one last hurrah for AM4, to give DDR5 a chance to be available, and performant compared to DDR4. A double release towards the end of this year of the AM5 platform and one last CPU for AM4 would be perfect for the market. But who knows...

they simply wouldnt be able to get enough stock for sales of AM5 when it needs new CPUs, mobos and RAM, if they abandon AM4

So AM4 should get one last hurrah, a zen3+ to keep using the existing stock and keep sales up while preparing stock for AM5 as a lower quantity, high priced premium option for early adopters... if you know you're gunna sell less products, market them as premium and up the price

We also have those x570S chipset boards coming out, so we know the sockets not abandoned... why release new mobo chipsets and whole new series of boards from multiple vendors, if no new CPUs are coming?

So many details are floating around regarding AM5, I'd expect it to launch this year, but only for APUs (Rembrandt/Zen3+). Not as a premium option. APU users aren't the most demanding crowd, they can tolerate the initial quirks and non-optimum performance of the whole AM5 + DDR5 platform, including high RAM latencies, but graphics would benefit a lot from the DDR5 bandwidth. 3D V-cache? No, that costs a lot. Gears? Sure, like in everything else on DDR5.

Come to think of that, AM5 may even begin its life in an OEM-only launch.

The last and best round of AM4 chips could arrive at the same time, maybe even after first ones on AM5. 3D V-cache? Yes, and that costs a lot, so the CPUs will cost a lot too. About 20% or 25% more for 15% more performance, says the law of diminishing returns.Well possibly - AMD can do all kinds of weird experiments, it's their chips. But don't take it for granted that it's possible to make an operative Ryzen CPU with asymmetrical configuration of cache. The one that Lisa showed could have been made just for her, that is, for showing off.

For testing without much hassle, AMD can build pairs of identical systems, with the only difference being the presence or absence of V-cache on both dies.

One of the most impressive bits of info was that the Zen 3 CCD was designed from the very beginning to be coupled with a stacked piece of cache. Anandtech reported that I think, and it really couldn't be another way, because you can't just put some extra static RAM on top of any random CPU and hope to connect it properly.

it would sell like pancakes as no GPUs in sight