Intel and DARPA Develop Secure Structured ASIC Chips Made in the US

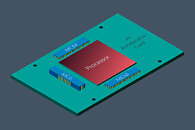

Intel and the U.S. Defense Advanced Research Projects Agency (DARPA) today announced a three-year partnership to advance the development of domestically manufactured structured Application Specific Integrated Circuit (ASIC) platforms. The Structured Array Hardware for Automatically Realized Applications (SAHARA) partnership enables the design of custom chips that include state-of-the-art security countermeasure technologies. A reliable, secure, domestic source of leading-edge semiconductors remains critical to the U.S.

"We are combining our most advanced Intel eASIC structured ASIC technology with state-of-the-art data interface chiplets and enhanced security protection, and it's all being made within the U.S. from beginning to end. This will enable defense and commercial electronics systems developers to rapidly develop and deploy custom chips based on Intel's advanced 10 nm semiconductor process," said José Roberto Alvarez, senior director, CTO Office, Intel Programmable Solutions Group.

"We are combining our most advanced Intel eASIC structured ASIC technology with state-of-the-art data interface chiplets and enhanced security protection, and it's all being made within the U.S. from beginning to end. This will enable defense and commercial electronics systems developers to rapidly develop and deploy custom chips based on Intel's advanced 10 nm semiconductor process," said José Roberto Alvarez, senior director, CTO Office, Intel Programmable Solutions Group.