Intel 20A and 18A Foundry Nodes Complete Development Phase, On Track for 2024 Manufacturing

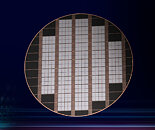

Intel Foundry Services, the in-house semiconductor foundry of Intel, announced that its 2 nm-class Intel 20A and 1.8 nm-class Intel 18A foundry nodes have completed development, and are on course for mass-producing chips on their roadmap dates. Chips are expected to begin mass-production on the Intel 20A node in the first half of 2024, while those on the Intel 18A node are expected to begin in the second half of 2024. The completion of the development phase means that Intel has finalized the specifications and performance/power targets of the nodes, the tools and software required to make the chips, and can now begin ordering them to build the nodes. Intel has been testing these nodes through 2022, and with the specs being finalized, chip-designers can accordingly wrap up development of their products to align with what these nodes have to offer.

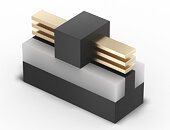

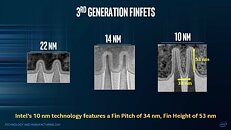

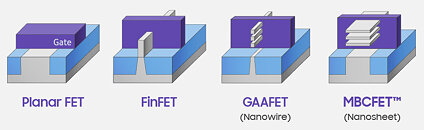

Intel 20A (or 20-angstrom, or 2 nm) node introduces gates-all-around (GAA) RibbonFET transistors with PowerVIAs (an interconnect innovation that contributes to transistor densities). The Intel 20A node is claimed to offer a 15% performance/Watt gain over its predecessor, the Intel 3 node (FinFET EUV, 3 nm-class), which by itself offers an 18% performance/Watt gain over Intel 4 (20% perf/Watt gain over the current Intel 7 node), the node that is entering mass-production very soon. The Intel 18A node is a further refinement of Intel 20A, and introduces a design improvement to the RibbonFET that increases transistor density at scale, and a claimed 10% performance/Watt improvement over Intel 20A.

Intel 20A (or 20-angstrom, or 2 nm) node introduces gates-all-around (GAA) RibbonFET transistors with PowerVIAs (an interconnect innovation that contributes to transistor densities). The Intel 20A node is claimed to offer a 15% performance/Watt gain over its predecessor, the Intel 3 node (FinFET EUV, 3 nm-class), which by itself offers an 18% performance/Watt gain over Intel 4 (20% perf/Watt gain over the current Intel 7 node), the node that is entering mass-production very soon. The Intel 18A node is a further refinement of Intel 20A, and introduces a design improvement to the RibbonFET that increases transistor density at scale, and a claimed 10% performance/Watt improvement over Intel 20A.