Monday, November 2nd 2020

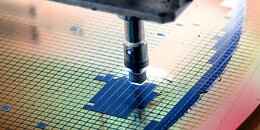

Samsung's 5 nm Node in Production, First SoCs to Arrive Soon

During its Q3 earnings call, Samsung Electronics has provided everyone with an update on its foundry and node production development. In the past year or so, Samsung's foundry has been a producer of a 7 nm LPP (Low Power Performance) node as its smallest node. That is now changed as Samsung has started the production of the 5 nm LPE (Low Power Early) semiconductor manufacturing node. In the past, we have reported that the company struggled with yields of its 5 nm process, however, that seems to be ironed out and now the node is in full production. To contribute to the statement that the new node is doing well, we also recently reported that Samsung will be the sole manufacturer of Qualcomm Snapdragon 875 5G SoC.

The new 5 nm semiconductor node is a marginal improvement over the past 7 nm node. It features a 10% performance improvement that is taking the same power and chip complexity or a 20% power reduction of the same processor clocks and design. When it comes to density, the company advertises the node with x1.33 times increase in transistor density compared to the previous node. The 5LPE node is manufactured using the Extreme Ultra-Violet (EUV) methodology and its FinFET transistors feature new characteristics like Smart Difusion Break isolation, flexible contact placement, and single-fin devices for low power applications. The node is design-rule compatible with the previous 7 nm LPP node, so the existing IP can be used and manufactured on this new process. That means that this is not a brand new process but rather an enhancement. First products are set to arrive with the next generation of smartphone SoCs, like the aforementioned Qualcomm Snapdragon 875.

Sources:

Samsung Q3 report, via Tom's Hardware

The new 5 nm semiconductor node is a marginal improvement over the past 7 nm node. It features a 10% performance improvement that is taking the same power and chip complexity or a 20% power reduction of the same processor clocks and design. When it comes to density, the company advertises the node with x1.33 times increase in transistor density compared to the previous node. The 5LPE node is manufactured using the Extreme Ultra-Violet (EUV) methodology and its FinFET transistors feature new characteristics like Smart Difusion Break isolation, flexible contact placement, and single-fin devices for low power applications. The node is design-rule compatible with the previous 7 nm LPP node, so the existing IP can be used and manufactured on this new process. That means that this is not a brand new process but rather an enhancement. First products are set to arrive with the next generation of smartphone SoCs, like the aforementioned Qualcomm Snapdragon 875.

4 Comments on Samsung's 5 nm Node in Production, First SoCs to Arrive Soon

Some of the other changes are coming from not just transistor gate pitch, but source and drain lines, how thick the insulting layers are, so yes, measuring the effective gate pitch is better at telling us power consumption. Not frequency scaling or slope. Cause everything is usually power limited.

TSMC has been ahead of Intel for a couple years now, maybe not on every aspect like density, but on power and as the new Ryzen ships are showing on performance with huge caches. Even though their IO chip is 12nm instead of 7.