Cervoz Announces T455 NVMe SSD Series - Offering Advanced Endurance for Demanding Industries

In industrial environments, equipment runs 24/7, handling frequent and intensive write operations. To support these demanding workloads, storage solutions must offer high endurance to extend lifespan, minimize downtime, and lower Total Cost of Ownership (TCO). Designed to meet these demands, the Cervoz T455 Series, M.2 2280 NVMe SSD delivers 35% greater endurance through a refined firmware architecture and proven storage technologies. Ideal for industrial automation, edge computing, and high-performance computing (HPC), it ensures reliable performance under heavy workloads.

Enhanced Endurance for Demanding Industrial Applications—Over-Provisioning Technology: Endurance SSD Performance and Longevity

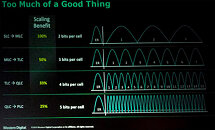

Cervoz's Over-Provisioning technology optimizes SSD performance by reserving extra storage space, boosting efficiency, and extending lifespan. How SSD Over-Provisioning Delivers Benefits:

Enhanced Endurance for Demanding Industrial Applications—Over-Provisioning Technology: Endurance SSD Performance and Longevity

Cervoz's Over-Provisioning technology optimizes SSD performance by reserving extra storage space, boosting efficiency, and extending lifespan. How SSD Over-Provisioning Delivers Benefits:

- Extended Lifespan: Efficiently reserves additional storage space, enhancing NAND durability at least 35%.

- Consistent Performance: Maintains steady performance levels even under high-intensity workloads.

- Optimized Resource Management: Reserved space allocation for optimal write efficiency.