Tuesday, August 27th 2019

Toshiba Talks About 5-Bit-per-Cell (PLC) Flash Memory

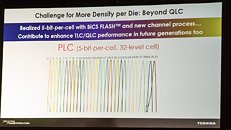

Toshiba at the Flash Memory Summit announced they've managed to develop a 5-Bit-per-Cell memory solution Based on its BiCS 4 flash memory technologies, the feat was achieved using a modified module of Quad-Level Cell (QLC) memory. This shows the technology is not only feasible, but has room for improvement, since an adapted QLC technology will always be inferior to a natively-developed, Penta-Level Cell (PLC) solution.

To achieve this ability to store one extra bit of information per cell (compared to QLC), a new level of voltage refinement is required: the cell has to be able to change its state according to one of 32 voltage states, which, in turn, have to be read out correctly by the flash memory controller. This reduces the cell's performance and endurance (as does any increase in the number of bits per cell), and will require a number of solutions to mitigate and compensate for this reduced performance. However, density has become an increasing concern from manufacturers, hence the continued development of deeper, more variable voltage states that allow for even more information to be stored in the same silicon area. Higher density means cheaper solutions, but density increased in such a way has known trade-offs that have been much talked about ever since the transition from Single-Level Cell (SLC) up to the (nowadays ubiquitous) QLC.

Source:

Tom's Hardware

To achieve this ability to store one extra bit of information per cell (compared to QLC), a new level of voltage refinement is required: the cell has to be able to change its state according to one of 32 voltage states, which, in turn, have to be read out correctly by the flash memory controller. This reduces the cell's performance and endurance (as does any increase in the number of bits per cell), and will require a number of solutions to mitigate and compensate for this reduced performance. However, density has become an increasing concern from manufacturers, hence the continued development of deeper, more variable voltage states that allow for even more information to be stored in the same silicon area. Higher density means cheaper solutions, but density increased in such a way has known trade-offs that have been much talked about ever since the transition from Single-Level Cell (SLC) up to the (nowadays ubiquitous) QLC.

15 Comments on Toshiba Talks About 5-Bit-per-Cell (PLC) Flash Memory

TLC (with cache) will go to the premium consumer category, QLC $ cacheless TLC to mainstream, PLC budget.

It will allow manufacturers to increase their profits again.

SLC: $/GB

TLC w./ cache: $/GB

TLC cacheless: $/GB

QLC (slower cacheless version incoming later?): $/GB

PLC (slower cacheless version incoming later?): $/GB

QLC is already pushing it... but PLC ? Come'on ...

And when you do the math, it's only 25% more bits for same number of cells ( QLC is 33% more than TLC, and TLC 50% more than M(2)LC )

Diminishing returns ... for massive loss in endurance.

Totally not worth it.

It doesn't matter using QLC since any flash storages are still faster than HDD in reading.

Those some cache should be enough for normal writing.

It'll start to make you feel disappointed when you write data that larger than its cache.

But for PLC, I couldn't see a serious reason to go.

SSD that slower than HDD is useless. Like a pricey HDD.