MSI Rolls Out AMD 400-series BIOS Updates with "Zen 2" Microcode

MSI mid-March began quietly rolling out BIOS updates for its socket AM4 motherboards based on AMD 400-series chipset, with a very ominous BIOS change-log entry: "Support new upcoming AMD CPU." At first, we dismissed this for being the company's follow-up to its 6th March announcement of support for some of the newer Athlon processor models, namely the 220GE and 240GE. After updating our MSI B450 Gaming Pro Carbon AC with one of these BIOSes, however, we discovered a very interesting microcode string - AGESA COMBO-AM4 0.0.7.2.

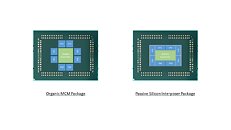

Such a major change in AGESA shouldn't be warranted to add support for two new chips based on existing "Raven Ridge" architecture that both AGESA "Summit Ridge" and AGESA PiR (Pinnacle Ridge) series microcodes should be able to comfortably run. We spoke with sources familiar with AMD microcode, who revealed that this AGESA COMBO-AM4 0.0.7.2 is designed for the upcoming "Zen 2" microarchitecture, and its first socket AM4 implementation, codenamed "Matisse." AMD internal versions of AGESA with Matisse support begin with the version sequence 0.0.7.x., and as we head closer to formal launch of these chips, AMD could release a 1.0.0.0 version of "AGESA COMBO-AM4." For our B450 Gaming Pro Carbon AC, the BIOS version packing this new AGESA is v1.60, and we wager this board should now be able to run Ryzen "Matisse" engineering samples. Now, if we can only get our hands on one.

Such a major change in AGESA shouldn't be warranted to add support for two new chips based on existing "Raven Ridge" architecture that both AGESA "Summit Ridge" and AGESA PiR (Pinnacle Ridge) series microcodes should be able to comfortably run. We spoke with sources familiar with AMD microcode, who revealed that this AGESA COMBO-AM4 0.0.7.2 is designed for the upcoming "Zen 2" microarchitecture, and its first socket AM4 implementation, codenamed "Matisse." AMD internal versions of AGESA with Matisse support begin with the version sequence 0.0.7.x., and as we head closer to formal launch of these chips, AMD could release a 1.0.0.0 version of "AGESA COMBO-AM4." For our B450 Gaming Pro Carbon AC, the BIOS version packing this new AGESA is v1.60, and we wager this board should now be able to run Ryzen "Matisse" engineering samples. Now, if we can only get our hands on one.