Intel Clearwater Forest Pictured, First 18A Node High Volume Product

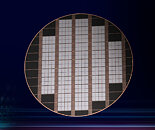

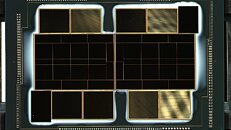

Yesterday, Intel launched its Xeon 6 family of server processors based on P-cores manufactured on Intel 3 node. While the early reviews seem promising, Intel is preparing a more advanced generation of processors that will make or break its product and foundry leadership. Codenamed "Clearwater Forest," these CPUs are expected to be the first high-volume production chips based on the Intel 18A node. We have pictures of the five-tile Clearwater Forest processor thanks to Tom's Hardware. During the Enterprise Tech Tour event in Portland, Oregon, Tom's Hardware managed to take a picture of the complex Clearwater Forest design. With compute logic built on 18A, this CPU uses Intel's 3-T process technology, which serves as the foundation for the base die, marking its debut in this role. Compute dies are stacked on this base die, making the CPU building more complex but more flexible.

The Foveros Direct 3D and EMIB technologies enable large-scale integration on a package, achieving capabilities that previous monolithic single-chip designs could not deliver. Other technologies like RibbonFET and PowerVia will also be present for Clearwater Forest. If everything continues to advance according to plan, we expect to see this next-generation CPU sometime next year. However, it is crucial to note that if this CPU shows that the high-volume production of Intel 18A is viable, many Intel Foundry customers would be reassured that Intel can compete with TSMC and Samsung in producing high-performance silicon on advanced nodes at scale.

The Foveros Direct 3D and EMIB technologies enable large-scale integration on a package, achieving capabilities that previous monolithic single-chip designs could not deliver. Other technologies like RibbonFET and PowerVia will also be present for Clearwater Forest. If everything continues to advance according to plan, we expect to see this next-generation CPU sometime next year. However, it is crucial to note that if this CPU shows that the high-volume production of Intel 18A is viable, many Intel Foundry customers would be reassured that Intel can compete with TSMC and Samsung in producing high-performance silicon on advanced nodes at scale.