Tuesday, August 11th 2009

Intel, Micron Achieve Industry's Most Efficient NAND Product Using 3-Bit/Cell Tech

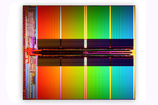

Intel Corporation and Micron Technology Inc. today announced the development of a new 3-bit-per-cell (3bpc) multi-level cell (MLC) NAND technology, leveraging their award-winning 34-nanometer (nm) NAND process. The chips are typically used in consumer storage devices such as flash cards and USB drives, where high density and cost-efficiency are paramount.

Designed and manufactured by IM Flash Technologies (IMFT), their NAND flash joint venture, the new 3bpc NAND technology produces the industry's smallest and most cost-effective 32-gigabit (Gb) chip that is currently available on the market. The 32Gb 3bpc NAND chip is 126 sq.mm. Micron is currently sampling and will be in mass production in the fourth quarter 2009. With the companies' continuing to focus on the next process shrink, 3bpc NAND technology is an important piece of their product strategy and is an effective approach in serving key market segments."We see 3bpc NAND technology as an important piece of our roadmap," said Brian Shirley, vice president of Micron's memory group. "We also continue to move forward on further shrinks in NAND that will provide our customers with a world-leading portfolio of products for many years to come. Today's announcement further highlights that Micron and Intel have made great strides in 34-nanometer NAND, and we look forward to introducing our 2xnm technology later this year."

"The move to 3bpc is yet another proof point to the remarkable progress Intel and Micron have made in 34-nm NAND development," said Randy Wilhelm, Intel vice president and general manager, Intel NAND Solutions Group. "This milestone sets the stage for continued silicon leadership on 2xnm process that will help decrease costs and increase the capabilities of our NAND solutions for our customers."

Designed and manufactured by IM Flash Technologies (IMFT), their NAND flash joint venture, the new 3bpc NAND technology produces the industry's smallest and most cost-effective 32-gigabit (Gb) chip that is currently available on the market. The 32Gb 3bpc NAND chip is 126 sq.mm. Micron is currently sampling and will be in mass production in the fourth quarter 2009. With the companies' continuing to focus on the next process shrink, 3bpc NAND technology is an important piece of their product strategy and is an effective approach in serving key market segments."We see 3bpc NAND technology as an important piece of our roadmap," said Brian Shirley, vice president of Micron's memory group. "We also continue to move forward on further shrinks in NAND that will provide our customers with a world-leading portfolio of products for many years to come. Today's announcement further highlights that Micron and Intel have made great strides in 34-nanometer NAND, and we look forward to introducing our 2xnm technology later this year."

"The move to 3bpc is yet another proof point to the remarkable progress Intel and Micron have made in 34-nm NAND development," said Randy Wilhelm, Intel vice president and general manager, Intel NAND Solutions Group. "This milestone sets the stage for continued silicon leadership on 2xnm process that will help decrease costs and increase the capabilities of our NAND solutions for our customers."

4 Comments on Intel, Micron Achieve Industry's Most Efficient NAND Product Using 3-Bit/Cell Tech

what the hell does 3 bits per cell mean anyway

And this technology isn't for SSDs.

if this makes higher density flash based mp3 players and flash keys more common and cheaper im all for it. :toast: