Tuesday, August 23rd 2016

AMD Details ZEN Microarchitecture IPC Gains

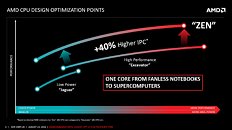

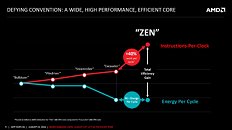

AMD Tuesday hosted a ZEN microarchitecture deep-dive presentation in the backdrop of Hot Chips, outlining its road to a massive 40 percent gain in IPC (translated roughly as per-core performance gains), over the current "Excavator" microarchitecture. The company credits the gains to three major changes with ZEN: better core engine, better cache system, and lower power. With ZEN, AMD pulled back from its "Bulldozer" approach to cores, in which two cores share certain number-crunching components to form "modules," and back to a self-sufficient core design.

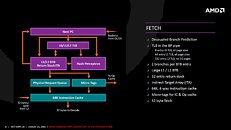

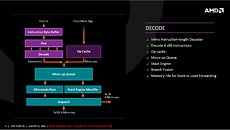

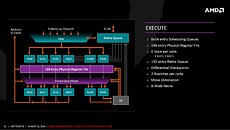

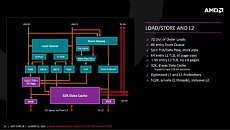

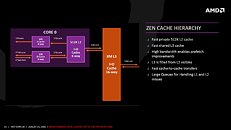

Beyond cores, the next-level subunit of the ZEN architecture is the CPU-Complex (CCX), in which four cores share an 8 MB L3 cache. This isn't different from current Intel architectures, the cores share nothing beyond L3 cache, making them truly independent. What makes ZEN a better core, besides its independence from other cores, and additional integer pipelines; subtle upscaling in key ancillaries such as micro-Op dispatch, instruction schedulers; retire, load, and store queues; and a larger quad-issue FPU.AMD also improved the cache system. The hierarchy is similar to pre-Bulldozer AMD architectures, with L3 cache being shared between full-fledged cores, and each core having a dedicated L2 cache. The L1 cache is now write-back (and not write-through), the SRAM that makes up the L2 and L3 caches are faster.The L3 cache SRAM has 5 times higher bandwidth than the L3 cache found on current AMD architectures. The L1 and L2 caches have 2 times the bandwidth. Load from cache to FPU is now faster. The core is endowed with 64 KB each of L1I cache, 32 KB L1D cache; 512 KB of dedicated L2 cache, and 8 MB of L3 cache shared between four cores in a CCX.ZEN introduces simultaneous multi-threading (SMT) to AMD processors. Intel's SMT implementation is the popular HyperThreading Technology. AMD's SMT is similar in that each core is addressed to as two threads, with each thread competing for the resources on the core.The third key area is lower-power, and this is attributed not just to the silicon-level gains yielded from the move to the 14 nm FinFET process. The design team focused on power-draw from the very inception of the ZEN core project. The L1 write-back cache, and the Op cache lower power-draw; the various components on ZEN processors feature aggressive clock-gating, although there's no power-gating.AMD expanded the ISA CPU instruction-sets, with AVX, AVX2, BMI1, BMI2, AES, RDRAND, sMEP, SHA1/SHA256, ADX, CFLUSHopt, XSAVEC/XSAVES/XRSTORS, and SMAP. The company also introduced a few AMD-exclusive instruction sets, which can be taken advantage of for better performance, including CLzero, and PTE Coalescing.

Beyond cores, the next-level subunit of the ZEN architecture is the CPU-Complex (CCX), in which four cores share an 8 MB L3 cache. This isn't different from current Intel architectures, the cores share nothing beyond L3 cache, making them truly independent. What makes ZEN a better core, besides its independence from other cores, and additional integer pipelines; subtle upscaling in key ancillaries such as micro-Op dispatch, instruction schedulers; retire, load, and store queues; and a larger quad-issue FPU.AMD also improved the cache system. The hierarchy is similar to pre-Bulldozer AMD architectures, with L3 cache being shared between full-fledged cores, and each core having a dedicated L2 cache. The L1 cache is now write-back (and not write-through), the SRAM that makes up the L2 and L3 caches are faster.The L3 cache SRAM has 5 times higher bandwidth than the L3 cache found on current AMD architectures. The L1 and L2 caches have 2 times the bandwidth. Load from cache to FPU is now faster. The core is endowed with 64 KB each of L1I cache, 32 KB L1D cache; 512 KB of dedicated L2 cache, and 8 MB of L3 cache shared between four cores in a CCX.ZEN introduces simultaneous multi-threading (SMT) to AMD processors. Intel's SMT implementation is the popular HyperThreading Technology. AMD's SMT is similar in that each core is addressed to as two threads, with each thread competing for the resources on the core.The third key area is lower-power, and this is attributed not just to the silicon-level gains yielded from the move to the 14 nm FinFET process. The design team focused on power-draw from the very inception of the ZEN core project. The L1 write-back cache, and the Op cache lower power-draw; the various components on ZEN processors feature aggressive clock-gating, although there's no power-gating.AMD expanded the ISA CPU instruction-sets, with AVX, AVX2, BMI1, BMI2, AES, RDRAND, sMEP, SHA1/SHA256, ADX, CFLUSHopt, XSAVEC/XSAVES/XRSTORS, and SMAP. The company also introduced a few AMD-exclusive instruction sets, which can be taken advantage of for better performance, including CLzero, and PTE Coalescing.

80 Comments on AMD Details ZEN Microarchitecture IPC Gains

Thanks for waking up early and posting this, Tarun. :toast:

This really got me even more excited for Zen

That's why AMD64 coexist with x86 instructions.

www.kitguru.net/components/cpu/anton-shilov/amd-clarifies-cross-license-with-intel-change-of-control-terminates-agreement-for-both/

www.theinquirer.net/inquirer/opinion/2253532/amd-looks-to-hsa-foundation-to-avoid-amd64-mistakes

www.cnet.com/news/intel-ftc-settle-antitrust-case/

web.archive.org/web/20000302151607/http://www1.amd.com/newsroom/display/1,1528,435,00.html

Anandtech has a 'discussion' on their recent PR, mostly around the Blender bench and explain what may be happening. AT says they (AMD) aren't being as hyperbolic as Bulldozer release and are vague enough with the benchmark as to keep things within expectations.

But as said, this keeps investors happy. They all do it (Intel, Nvidia), so it's not an AMD peculiarity.

40% is what i would think is a bare minimum to compete with today's intel's IPC

And we have yet to see what AMD will really cook up with it.

That said, if you have a link that shows October, post it up!Your point? Did you quote the wrong person? He didn't say nor allude to that fact. He is looking for better than Intel performance. ;)

Or maybe lower power allows them to use more complex cores.