Tuesday, March 7th 2017

AMD "Naples" is a 32-core Zen Based Monstrosity

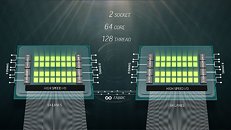

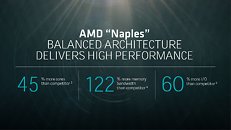

AMD today unveiled the "Naples" enterprise processor, and it is big. The chip could mark AMD's return to competitive enterprise CPUs after years. The first "Naples" based part has some staggering specifications - 32 CPU cores spread across eight CCX units, SMT enabling 64 threads, an octa-channel (yes, eight channels) DDR4 integrated memory controller, an industry-leading 64-lane PCI-Express gen 3.0 root complex, and AMD's new Infinity Fabric interconnect, which lets it talk to the neighboring CPU, in a 2P system. The IMC supports up to 2 TB of memory.

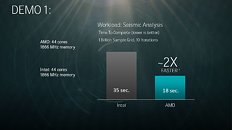

AMD will competitively price "Naples" against Intel's Xeon E5-2600 series 2P chips, offering more cores, wider memory interfaces, more memory support, and more PCIe lanes. AMD will tap into the good energy-efficiency of its "Zen" architecture to clock these chips competitively higher than Intel chips, to churn out more overall performance. AMD is scheduled to launch the first processors based on the "Naples" silicon, within Q2-2017."Today marks the first major milestone in AMD re-asserting its position as an innovator in the datacenter and returning choice to customers in high-performance server CPUs," said Forrest Norrod, senior vice president and general manager, Enterprise, Embedded and Semi-Custom business unit, AMD. "'Naples' represents a completely new approach to supporting the massive processing requirements of the modern datacenter. This groundbreaking system-on-chip delivers the unique high-performance features required to address highly virtualized environments, massive data sets and new, emerging workloads."

AMD will competitively price "Naples" against Intel's Xeon E5-2600 series 2P chips, offering more cores, wider memory interfaces, more memory support, and more PCIe lanes. AMD will tap into the good energy-efficiency of its "Zen" architecture to clock these chips competitively higher than Intel chips, to churn out more overall performance. AMD is scheduled to launch the first processors based on the "Naples" silicon, within Q2-2017."Today marks the first major milestone in AMD re-asserting its position as an innovator in the datacenter and returning choice to customers in high-performance server CPUs," said Forrest Norrod, senior vice president and general manager, Enterprise, Embedded and Semi-Custom business unit, AMD. "'Naples' represents a completely new approach to supporting the massive processing requirements of the modern datacenter. This groundbreaking system-on-chip delivers the unique high-performance features required to address highly virtualized environments, massive data sets and new, emerging workloads."

59 Comments on AMD "Naples" is a 32-core Zen Based Monstrosity

4 dual channel memory controllers for "octa channel" memory. So memory bandwidth real world will likely be nothing like the 6 channel Intel chips.

That's not to say performance will be bad, but it is definitely not an octa channel setup as it is quoted. Not in the normal sense.

The communication between Cpus has me very very interested. 64 pcie lanes talking between each cpu is an interesting idea.

I am excited for q2 and hope I can snatched up an ES for testing.

It's not PCI-e lanes talking, it's "Data Fabric" that does the talking, they're using the PCI-E controllers for it, how is what I'm curious about.

Now your losing half the chips pciex lanes, it's 128, 64 are used just for socket to socket communication, over pciex using their infinity fabric protocol.

Now the ram could operate in a different manner than I am assuming, but considering they are using the same CCX units as the ryzen chip and just adding more of them I strongly doubt that it is anymore than 4 dual channel controllers teamed together for "octa channel" memory in the same exact way they have done for bulldozer/piledriver based units.

Per chip that's 128 and to be fair I disagree on the memory yeah but I'm not saying I'm definitely right just that given what they're saying it's what I believe but I won't argue that point because not many know for sure , you could be right though.

As far as it goes it would be very sensible if it did have quad channels to not use them in consumer land on a first generation chip, especially to help binning yealds.

@cdawall on this one.

I'm going to wait.

You really need to utilitize that to get the very best out of it, it's a different tactic then intels real quad memory controller. But since servers move lots of data, i'm sure it will be fine.

AMD has less R&D to actually develop a much better server version for ZEN, so it's sticking to a larger design then what consumers get. And by looking at those benchmarks i'm sure the chip will do fine.

Lets hope there is sufficient memory kits available for server enviroments offering decent speeds. The ZEN scales much better as memory speeds go up to 3200.