Friday, April 6th 2018

Intel Could Develop its own big.LITTLE x86 Adaptation

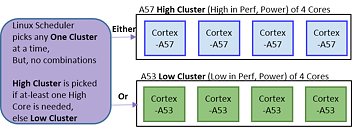

big.LITTLE is an innovation by ARM, which seeks to minimize power-draw on mobile devices. It is a sort of heterogeneous multi-core CPU design, in which a few "big" high-performance CPU cores work alongside a few extremely low-power "little" CPU cores. The idea here is that the low-power cores consume much lesser power at max load, than the high-performance cores at their minimum power-state, so the high-performance cores can be power-gated when the system doesn't need them (i.e. most of the time).

Intel finds itself with two distinct x86 implementations at any given time. It has low-power CPU micro-architectures such as "Silvermont," "Goldmont," and "Goldmont Plus," etc., implemented on low-power product lines such as the Pentium Silver series; and it has high-performance micro-architectures, such as "Haswell," "Skylake," and "Coffee Lake." The company wants to take a swing at its own heterogeneous multi-core CPU, according to tech stock analyst Ashraf Eassa, with the Motley Fool.Codenamed "Lakefield," this chip combines "Ice Lake" high-performance cores with "Tremont" low-power cores. The "Ice Lake" micro-architecture is expected to power Intel's 10th generation Core processors, and succeeds both "Coffee Lake" and "Cannon Lake." The "Tremont" micro-architecture, on the other hand, succeeds the current "Goldmont Plus" micro-architecture. This chip could have a great many potential applications with high-end notebooks and 2-in-1s, in which the device can benefit from the battery-life of low-power SoC based devices, and the high-end performance when needed.

A chip like this would need popular operating systems to be redesigned to be aware of the asymmetry. That would involve changes to the kernel scheduler, so it could know which threads to send to which cores. Given that Intel's 10 nm process, on which "Ice Lake" is based, is scheduled for a 2019-20 roll-out, "Lakefield" chip may not see a launch this year.

Source:

Ashraf Eassa (Twitter)

Intel finds itself with two distinct x86 implementations at any given time. It has low-power CPU micro-architectures such as "Silvermont," "Goldmont," and "Goldmont Plus," etc., implemented on low-power product lines such as the Pentium Silver series; and it has high-performance micro-architectures, such as "Haswell," "Skylake," and "Coffee Lake." The company wants to take a swing at its own heterogeneous multi-core CPU, according to tech stock analyst Ashraf Eassa, with the Motley Fool.Codenamed "Lakefield," this chip combines "Ice Lake" high-performance cores with "Tremont" low-power cores. The "Ice Lake" micro-architecture is expected to power Intel's 10th generation Core processors, and succeeds both "Coffee Lake" and "Cannon Lake." The "Tremont" micro-architecture, on the other hand, succeeds the current "Goldmont Plus" micro-architecture. This chip could have a great many potential applications with high-end notebooks and 2-in-1s, in which the device can benefit from the battery-life of low-power SoC based devices, and the high-end performance when needed.

A chip like this would need popular operating systems to be redesigned to be aware of the asymmetry. That would involve changes to the kernel scheduler, so it could know which threads to send to which cores. Given that Intel's 10 nm process, on which "Ice Lake" is based, is scheduled for a 2019-20 roll-out, "Lakefield" chip may not see a launch this year.

36 Comments on Intel Could Develop its own big.LITTLE x86 Adaptation

BTW, patching existing software may just be impossible with many software IMHO, considering the fact that a big.LITTLE AVX implementation would require major changes in a way how software manages computation threads and explicit thread affinity. You cannot just launch a thread in a mixed-ISA system and rely on the OS to figure out which CPU core can execute the instructions coming up in that computation thread. You need to explicitly iterate through the available CPU cores, detect which one supports AVX, AVX2 or AVX512, and launch a suitable thread on each core by assigning the thread explicitly to that particular CPU core. Otherwise a thread running AVX code may be re-assigned by the OS scheduler to a non-AVX-capable core, etc. etc. Nightmare, really, especially if you have a simple software that only detects AVX capability once, and then just launches an AVX computation task without hassling with thread affinity and other ISA awareness.

Anyway, that's for Intel to figure out, I don't think we need to worry about it here on TPU.

+/*TODO: implement topdown metrics, base metrics interface same as SNC */

+x86_pmu.cpu_events = tnt_events_attrs;

+

+pr_cont("Tremont events, ");

+break;

initconst const u64 tnt_hw_cache_event_ids

tnt in the patch is Tremont.

honestly i dare to bet they got the idea of big.LITTLE after looking at nvidia "ninja core" inside tegra 3.

Have 2 x atom cores in a core2 duo.

Then after some research etc looked like it might be possible.

Found out about arm and some mips chips with similar setups.