Thursday, July 12th 2018

DARPA to Dedicate $100 million to EDA Projects Over the Next Five Years

EDA (Electronic Design Automation) is a quintessential part of modern silicon processor design - of any kind. Be it GPUs, CPUs, or SOCs, you can bet an electronic design tool has been applied somewhere in the process. These tools serve their function in various steps of silicon design, be it allowing for automated placement of components, signal routing, power optimization, and analyzing said designs with performance and bottleneck projections. It was rumored that Bulldozer was such a flawed architecture due to the overuse (and misuse) of EDA tools in its design; but mostly, usage of these tools is done in conjunction with engineers' hand-crafted, manually laid-out circuits.

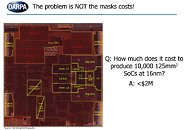

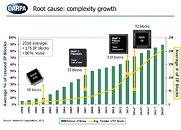

In an effort to accelerate development and reduce cost of chip design (now approaching $500 million for a bleeding-edge SoC), two programs, IDEA (Intelligent Design of Electronic Assets) and POSH (Posh Open Source Hardware), involving 15 companies and more than 200 researchers, will receive $100 million in funding over the next five years. The IDEA is to create the equivalent of a silicon compiler, aimed at significantly lowering the barriers to design chips. POSH aims to create an open-source library of silicon blocks (that circuit designers can then mix and match according to their needs), and IDEA hopes to spawn a variety of open-source and commercial tools to automate testing of those blocks and actually grafting them into SoCs and finished products. Lower development costs means that lower-volume, specialized chips can now be developed more often, thus ushering a new era of specially-designed, fixed-function chips that are more efficient than mass-volume alternatives.

Sources:

EE Times, DARPA's ERI, IDEA and POSH Presentation PDF

In an effort to accelerate development and reduce cost of chip design (now approaching $500 million for a bleeding-edge SoC), two programs, IDEA (Intelligent Design of Electronic Assets) and POSH (Posh Open Source Hardware), involving 15 companies and more than 200 researchers, will receive $100 million in funding over the next five years. The IDEA is to create the equivalent of a silicon compiler, aimed at significantly lowering the barriers to design chips. POSH aims to create an open-source library of silicon blocks (that circuit designers can then mix and match according to their needs), and IDEA hopes to spawn a variety of open-source and commercial tools to automate testing of those blocks and actually grafting them into SoCs and finished products. Lower development costs means that lower-volume, specialized chips can now be developed more often, thus ushering a new era of specially-designed, fixed-function chips that are more efficient than mass-volume alternatives.

"I've designed a few boards and found it excruciating," he said. "[Board designs quickly] explode into hundreds of details you have to worry about in resistors, capacitors, board size … and there are no optimization tools, so often, you have a sub-optimal solution. Given the number of boards designed every year, the upside here is enormous."The projects are scheduled for a tentative, first release window in 2020 aimed at producing chips not fully optimized for power, performance, or area - its objective is to present simpler designs than the end result, as a way to increase confidence in the project. Final results are slated for 2022 and target quality comparable to traditional design teams.The two projects have 11 teams each with a total of 70 industry members. Companies participating include ADI, ARM, Cadence, Northrup Grumman, Nvidia, Qualcomm, and Xilinx. Fifteen universities are also involved, contributing time from 44 professors and 99 grad students. They include Carnegie Mellon, The University of California at San Diego (UCSD), and the Universities of Illinois, Michigan, Texas, Utah, Virginia, and Washington.

Andreas Olofsson, IDEAS, POSH Program Manager

7 Comments on DARPA to Dedicate $100 million to EDA Projects Over the Next Five Years

I'm also wondering what type of CPU is it going to be built around? ARM? x86? Something new? Any, as part of the module design? If the bus is an open standard so any processor can be designed to hook into it, this DARPA project could lead to a revolution in SoC fabrication.

Why DARPA? Because US military uses a lot of SoC and they aim to be able to design exactly what they want for each application on the cheap.en.wikipedia.org/wiki/DARPA#Projects

Of particular note: HIVE CPU architecture, basically a security/analytical dedicated processor. RISC and BSD Unix were spawned off of the VLSI Project.

A lot of practical advancements in robotics are also funded by DARPA, for example, BigDog:

At least I think? Not exactly up to speed here.